NOTE: The cover page of this standard has

been changed for administrative reasons.

There are no other changes to this document.

**MIL-STD-188-114A**

**30 SEPTEMBER 1985**

---

**SUPERSEDING**

**MIL-STD-188-114**

**24 MARCH 1976**

## **DEPARTMENT OF DEFENSE INTERFACE STANDARD**

### **ELECTRICAL CHARACTERISTICS OF DIGITAL INTERFACE CIRCUITS**

**TCTS**

**NO DELIVERABLE

DATA REQUIRED BY

THIS DOCUMENT**

**APPROVED FOR PUBLIC

RELEASE; DISTRIBUTION

IS UNLIMITED**

MIL-STD-188-114A

30 September 1985

DEPARTMENT OF DEFENSE

Washington, DC 20301

Electrical Characteristics

of Digital Interface Circuits

MIL-STD-188-114A

1. This Military Standard is approved and mandatory for use by all Departments and Agencies of the Department of Defense, in accordance with the memorandum of the Under Secretary of Defense for Research and Engineering, dated 16 August 1983. (See Appendix A).

2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to:

Commander

U.S. Army Communications-Electronics Command

ATTN: AMSEL-SEI-I

Fort Monmouth, New Jersey 07703-5203

by using the self-addressed Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

MIL-STD-188-114A

30 September 1985

FOREWORD

1. Originally, Military Standard 188 (MIL-STD-188) covered technical standards for tactical and long haul communications, but later evolved through revisions (MIL-STD-188A, MIL-STD-188B) into a document applicable to tactical communications only (MIL-STD-188C).

2. The Defense Communications Agency (DCA) published DCA Circulars (DCAC) promulgating standards and engineering criteria applicable to the long haul Defense Communications System (DCS) and to the technical support of the National Military Command System (NMCS).

3. As a result of a Joint Chiefs of Staff (JCS) action, standards for all military communications are now being published in a MIL-STD-188 series of documents. The MIL-STD-188 series is subdivided into a MIL-STD-188-100 series covering common standards for tactical and long haul communications, a MIL-STD-188-200 series covering standards for tactical communications only, and a MIL-STD-188-300 series covering standards for long haul communications only. Emphasis is being placed on developing common standards for tactical and long haul communications published in the MIL-STD-188-100 series.

4. This document contains electrical and functional characteristics of the unbalanced and balanced voltage digital interface circuits applicable to both long haul and tactical communications.

5. This document supersedes MIL-STD-188-114 which superseded subparagraph 4.3.1.3 of MIL-STD-188-100 and subparagraph 7.2.1 of MIL-STD-188C.

MIL-STD-188-114A

30 September 1985

IDENTIFICATION OF

INTERNATIONAL STANDARDIZATION AGREEMENT

Certain provisions of this document (see 4.7) are the subject of international standardization agreement QSTAG 594. When an amendment, revision, or cancellation of this standard is proposed which will modify the international agreement concerned, the preparing activity will take appropriate action through international standardization channels, including departmental standardization offices to change the agreement or make other appropriate accommodations.

ACKNOWLEDGEMENT

The Electronic Industries Association (EIA) is the copyright holder of material used in this document. Their permission to reproduce portions of EIA Standards RS-422A and RS-423A is gratefully acknowledged. These EIA standards may be purchased from the Electronics Industries Association (EIA), 2001 Eye Street, N.W., Washington, D.C., 20006.

**MIL-STD-188-114A**

30 September 1985

**CONTENTS**

| <u>Paragraph</u> | <u>Title</u>                                                      | <u>Page</u> |

|------------------|-------------------------------------------------------------------|-------------|

|                  | Promulgation sheet                                                | ii          |

|                  | Foreword                                                          | iii         |

|                  | Identification of International Standardization Agreement         | iv          |

|                  | Acknowledgement                                                   | iv          |

| 1                | SCOPE                                                             | 1           |

| 1.1              | Purpose                                                           | 1           |

| 1.2              | Application                                                       | 1           |

| 1.3              | System standards and design objectives                            | 3           |

| 2                | REFERENCED DOCUMENTS                                              | 4           |

| 2.1              | Government documents                                              | 4           |

| 2.1.1            | Standards                                                         | 4           |

| 2.1.2            | Other Government documents and publications                       | 4           |

| 2.2              | Order of precedence                                               | 4           |

| 3                | DEFINITIONS                                                       | 5           |

| 3.1              | Definitions                                                       | 5           |

| 3.2              | Abbreviations and acronyms                                        | 5           |

| 4                | GENERAL REQUIREMENTS                                              | 7           |

| 4.1              | Description of digital interface circuits                         | 7           |

| 4.2              | Description of functional interchange circuits                    | 7           |

| 4.3              | Signaling rate range                                              | 7           |

| 4.4              | Selection of type of digital interface circuit                    | 8           |

| 4.4.1            | Types of balanced generators                                      | 8           |

| 4.4.2            | Use of balanced voltage digital interface circuit                 | 8           |

| 4.4.3            | Use of balanced and unbalanced voltage digital interface circuits | 9           |

| 4.5              | Relationship with other digital interface standards               | 9           |

| 4.6              | Grounding requirements                                            | 9           |

| 4.7              | Interoperability requirements of ABCA Armies                      | 9           |

| 4.8              | Compromising emanations (TEMPEST) requirements                    | 10          |

MIL-STD-188-114A

30 September 1985

| <u>Paragraph</u> | <u>Title</u>                                 | <u>Page</u> |

|------------------|----------------------------------------------|-------------|

| 5                | DETAILED REQUIREMENTS                        | 11          |

| 5.1              | Unbalanced voltage digital interface circuit | 11          |

| 5.1.1            | Generator characteristics                    | 12          |

| 5.1.1.1          | Signal sense                                 | 12          |

| 5.1.1.2          | Signaling rate range                         | 12          |

| 5.1.1.3          | Open-circuit measurement                     | 12          |

| 5.1.1.4          | Test termination measurement                 | 14          |

| 5.1.1.5          | Short-circuit measurement                    | 14          |

| 5.1.1.6          | Power-off measurement                        | 14          |

| 5.1.1.7          | Output signal waveform                       | 15          |

| 5.1.1.8          | Output signal waveshaping                    | 15          |

| 5.1.1.9          | High impedance output state                  | 17          |

| 5.1.2            | Wire or cable characteristics                | 17          |

| 5.1.3            | Load characteristics                         | 17          |

| 5.1.3.1          | Receiver input current-voltage measurement   | 18          |

| 5.1.3.2          | Receiver input sensitivity measurement       | 18          |

| 5.1.3.3          | Receiver input balance measurement           | 18          |

| 5.1.3.4          | Multiple receivers                           | 18          |

| 5.1.3.5          | Fail safe operation                          | 20          |

| 5.1.3.6          | Total load characteristic limits             | 20          |

| 5.1.4            | Operational constraints                      | 20          |

| 5.1.5            | Circuit protection                           | 21          |

| 5.2              | Balanced voltage digital interface circuit   | 22          |

| 5.2.1            | Generator characteristics                    | 22          |

| 5.2.1.1          | Signal sense                                 | 22          |

| 5.2.1.2          | Signaling rate range                         | 22          |

| 5.2.1.3          | Open-circuit measurement                     | 22          |

| 5.2.1.4          | Test termination measurement                 | 25          |

| 5.2.1.5          | Short-circuit measurement                    | 25          |

| 5.2.1.6          | Power-off measurement                        | 25          |

| 5.2.1.7          | Output signal waveform                       | 25          |

| 5.2.1.8          | High impedance output state                  | 28          |

| 5.2.2            | Wire or cable characteristics                | 28          |

| 5.2.3            | Load characteristics                         | 28          |

| 5.2.3.1          | Receiver input current-voltage measurement   | 28          |

| 5.2.3.2          | Receiver input sensitivity measurement       | 28          |

| 5.2.3.3          | Receiver input balance measurement           | 28          |

| 5.2.3.4          | Multiple receivers                           | 28          |

| 5.2.3.5          | Fail safe operation                          | 29          |

| 5.2.3.6          | Total load characteristic limits             | 29          |

| 5.2.3.7          | Wire or cable termination resistance         | 29          |

| 5.2.4            | Operational constraints                      | 29          |

| 5.2.5            | Circuit protection                           | 30          |

| 5.3              | Terminated voltage digital interface circuit | 30          |

**MIL-STD-188-114A**

30 September 1985

| <u>Paragraph</u> | <u>Title</u>                               | <u>Page</u> |

|------------------|--------------------------------------------|-------------|

| 5.3.1            | Generator characteristics                  | 30          |

| 5.3.1.1          | Signal sense                               | 30          |

| 5.3.1.2          | Signaling rate range                       | 30          |

| 5.3.1.3          | Output voltage measurement                 | 30          |

| 5.3.1.4          | Balance measurement                        | 33          |

| 5.3.1.5          | Current measurements                       | 33          |

| 5.3.1.6          | Power-off test                             | 33          |

| 5.3.1.7          | Output signal waveform                     | 33          |

| 5.3.2            | Wire or cable characteristics              | 35          |

| 5.3.3            | Load characteristics                       | 35          |

| 5.3.3.1          | Receiver input current-voltage measurement | 35          |

| 5.3.3.2          | Receiver input sensitivity measurement     | 35          |

| 5.3.3.3          | Receiver input balance measurement         | 35          |

| 5.3.3.4          | Multiple receivers                         | 35          |

| 5.3.3.5          | Fail safe operation                        | 35          |

| 5.3.3.6          | Total load characteristic limits           | 35          |

| 5.3.3.7          | Wire or cable termination resistance       | 35          |

| 5.3.4            | Operational constraints                    | 35          |

| 5.3.5            | Circuit protection                         | 35          |

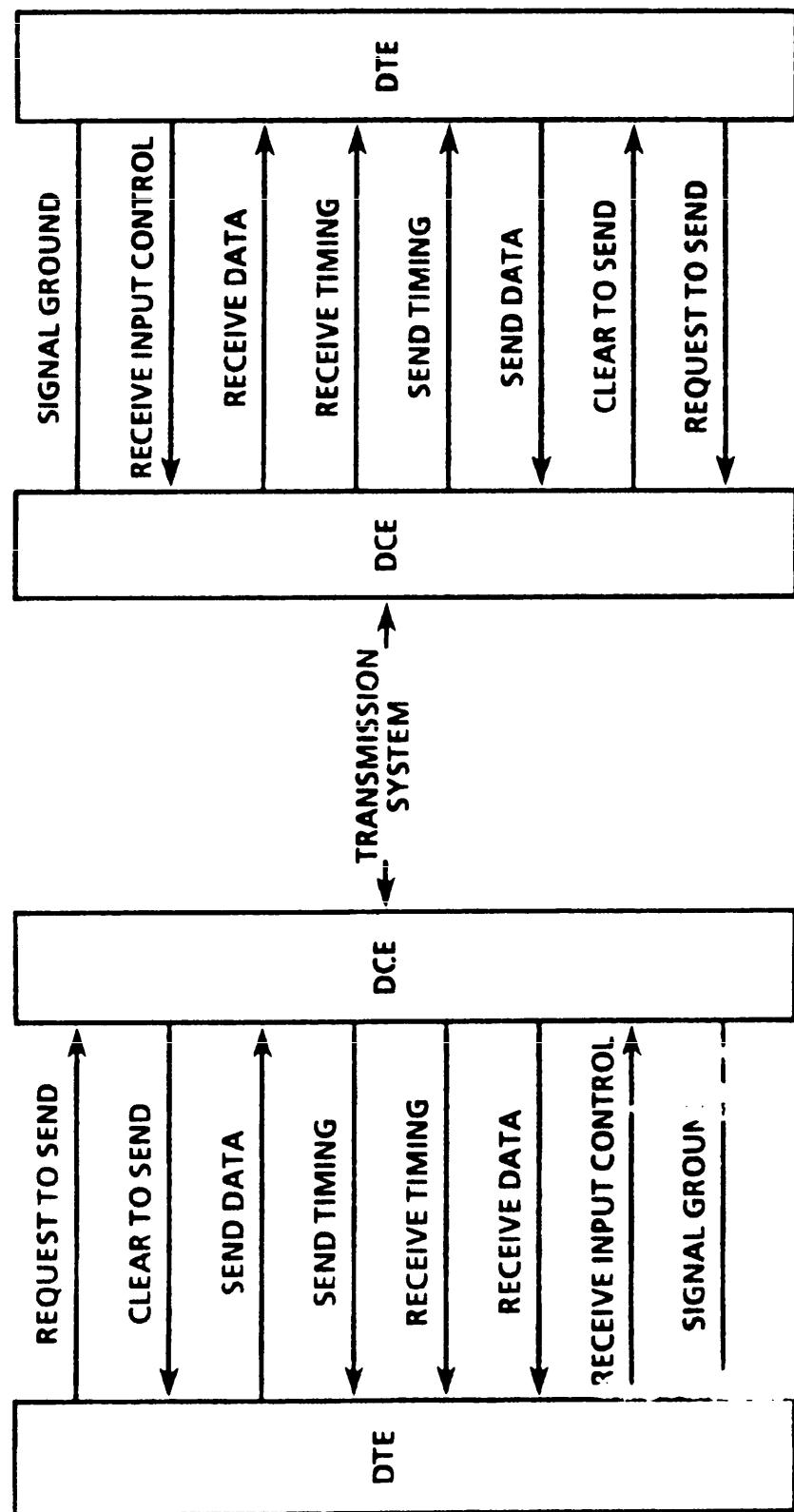

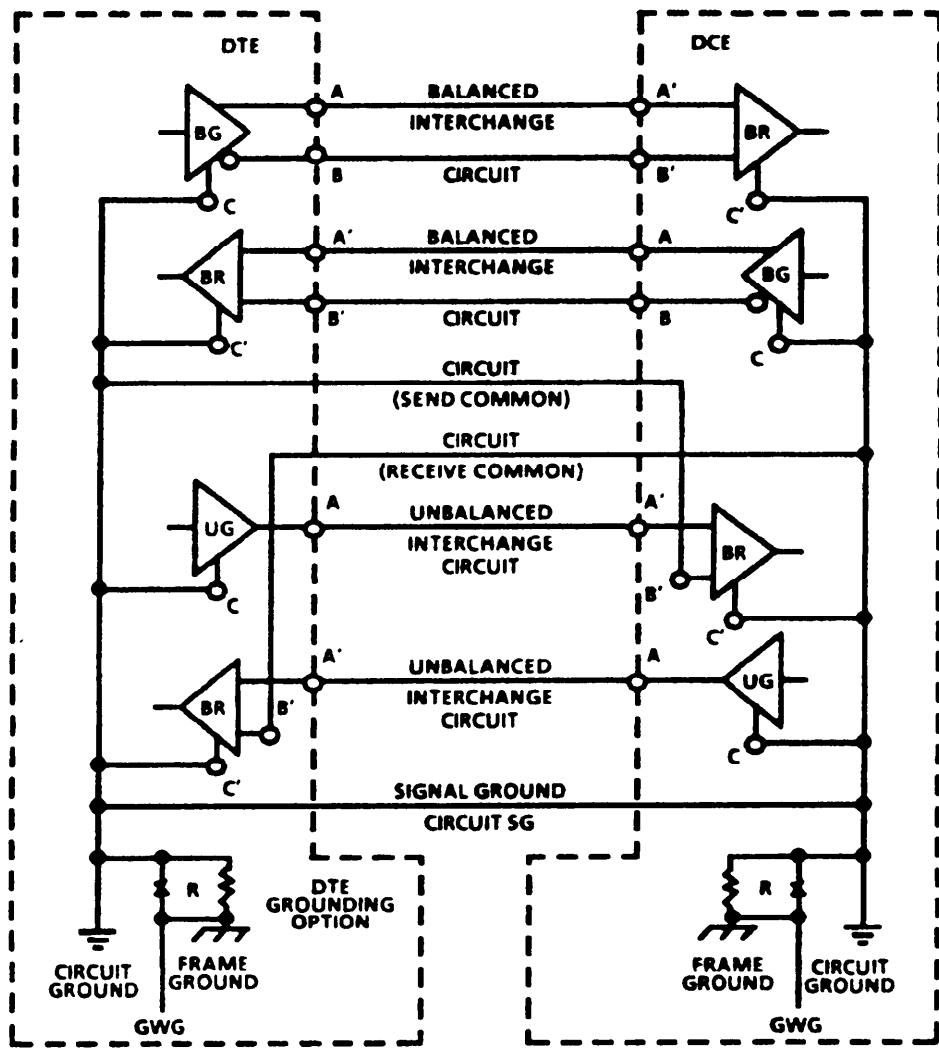

| 5.4              | Functional interchange circuits            | 35          |

| 5.4.1            | Interchange circuit requirements           | 35          |

| 5.4.2            | Interchange circuit functions              | 37          |

| 5.4.2.1          | Request to send                            | 37          |

| 5.4.2.2          | Clear to send                              | 37          |

| 5.4.2.3          | Receive input control                      | 37          |

| 5.4.2.4          | Send data                                  | 37          |

| 5.4.2.5          | Receive data                               | 37          |

| 5.4.2.6          | Send timing                                | 38          |

| 5.4.2.7          | Receive timing                             | 38          |

| 5.4.2.8          | Send common                                | 38          |

| 5.4.2.9          | Receive common                             | 38          |

| 5.4.2.10         | Signal ground                              | 38          |

MIL-STD-188-114A

30 September 1985

FIGURES

| <u>Number</u> | <u>Title</u>                                                                                    | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------|-------------|

| 1             | Block diagram of data terminal subsystem                                                        | 2           |

| 2             | Unbalanced voltage digital interface circuit                                                    | 11          |

| 3             | Unbalanced generator parameter measurements                                                     | 13          |

| 4             | Nominal waveform of unbalanced generator                                                        | 14          |

| 5             | Unbalanced generator output signal waveform                                                     | 16          |

| 6             | Example method for waveshaping of unbalanced voltage digital interface circuit                  | 17          |

| 7             | Receiver input current-voltage measurement                                                      | 19          |

| 8             | Receiver input sensitivity measurement                                                          | 19          |

| 9             | Receiver input balance measurement                                                              | 20          |

| 10            | Balanced voltage digital interface circuit                                                      | 23          |

| 11            | Balanced generator parameter measurements                                                       | 24          |

| 12            | Nominal waveforms of type I and type II generators                                              | 26          |

| 13            | Balanced generator output signal waveform                                                       | 27          |

| 14            | Terminated voltage digital interface circuit                                                    | 31          |

| 15            | Terminated voltage generator parameter measurements                                             | 32          |

| 16            | Terminated voltage generator output signal waveform                                             | 34          |

| 17            | Example of functional interchange circuits                                                      | 36          |

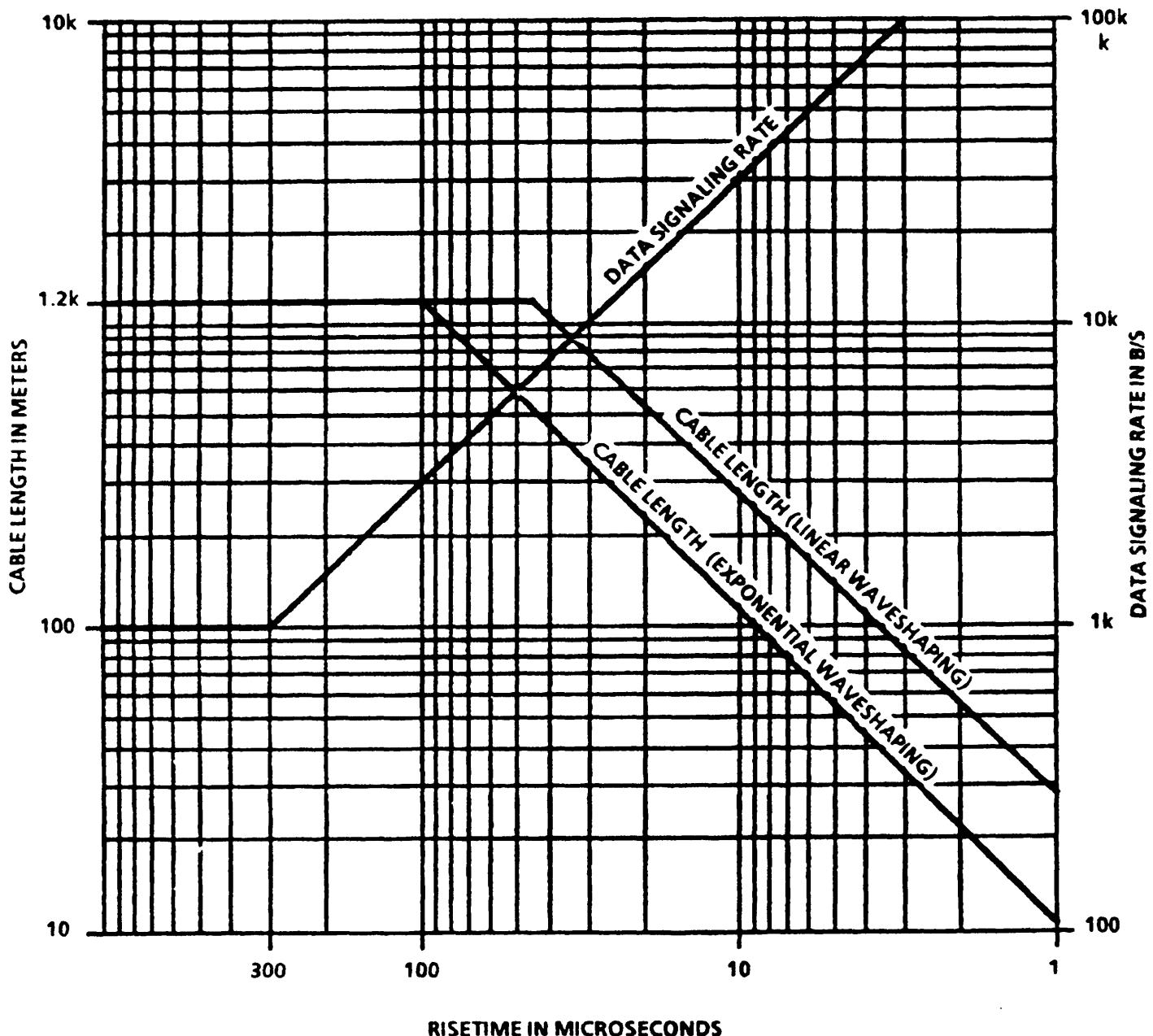

| 18            | Signaling rate or cable length versus risetime for unbalanced voltage digital interface circuit | 45          |

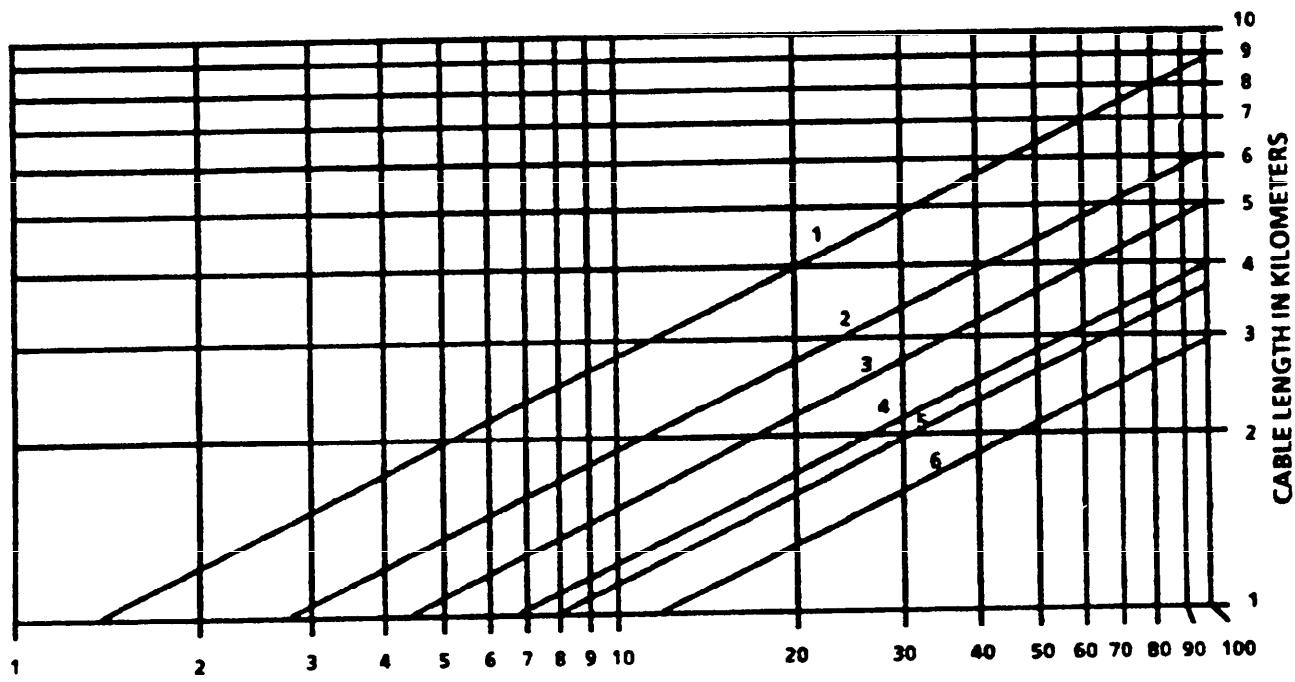

| 19            | Cable pair RC time constant versus cable length                                                 | 47          |

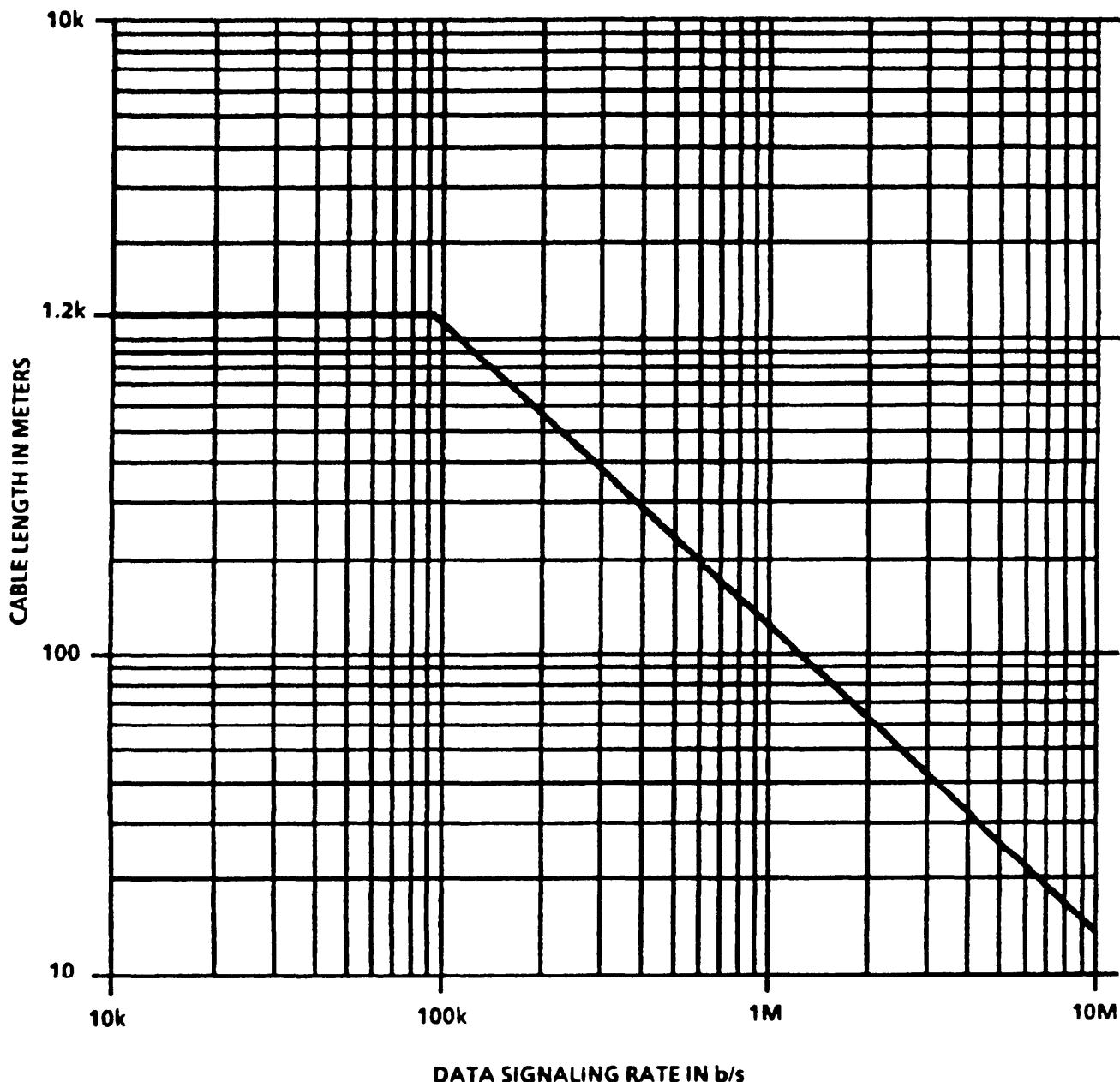

| 20            | Signaling rate versus cable length for balanced voltage digital interface circuit               | 48          |

MIL-STD-188-114A

30 September 1985

| <u>Number</u> | <u>Title</u>                                                                                | <u>Page</u> |

|---------------|---------------------------------------------------------------------------------------------|-------------|

| 21            | Example method of fail-safe for unbalanced voltage digital interface circuit                | 51          |

| 22            | Example method of fail-safe for balanced voltage digital interface circuit                  | 52          |

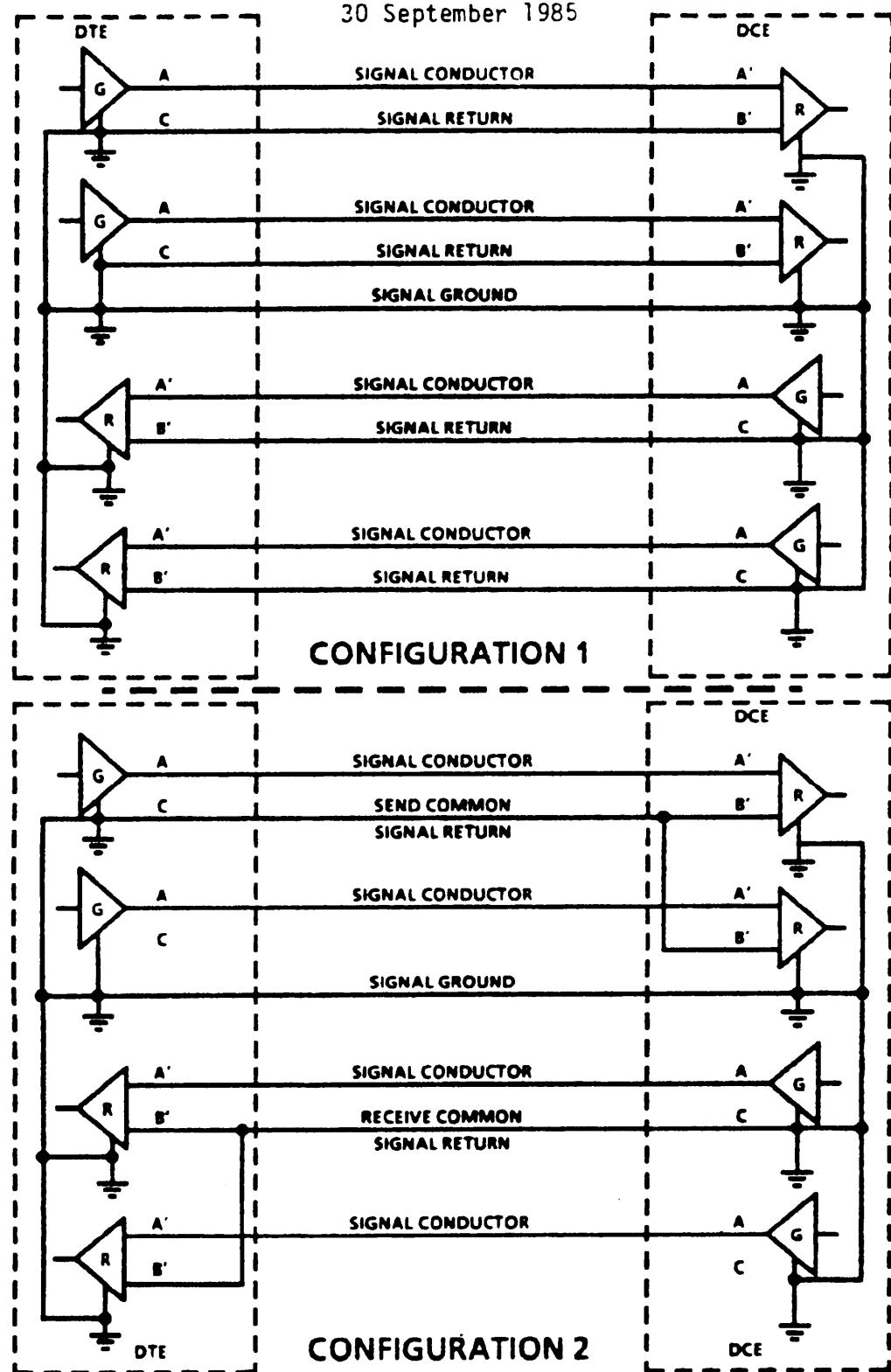

| 23            | Examples of optional grounding arrangements                                                 | 54          |

| 24            | Interconnection of signal common return for unbalanced voltage digital interface circuit    | 56          |

| 25            | Unbalanced generator driving unbalanced receiver                                            | 60          |

| 26            | Unbalanced generator driving balanced receiver without inversion of MARK-SPACE signal sense | 60          |

| 27            | Unbalanced generator driving balanced receiver with inversion of MARK-SPACE signal sense    | 61          |

| 28            | Unbalanced generator driving balanced wire pair with balanced receiver                      | 61          |

| 29            | Balanced generator driving balanced receiver                                                | 62          |

| 30            | Balanced generator driving unbalanced receiver                                              | 62          |

TABLES

| <u>Number</u> | <u>Title</u>                                                                                | <u>Page</u> |

|---------------|---------------------------------------------------------------------------------------------|-------------|

| I             | Signal sense for unbalanced generators                                                      | 12          |

| II            | Signal sense for balanced generators                                                        | 22          |

| III           | Functional interchange circuits                                                             | 37          |

| IV            | Interoperation among devices complying with different low level digital interface standards | 63          |

MIL-STD-188-114A

30 September 1985

APPENDICES

| <u>Appendix</u>  | <u>Title</u>                                                                                                                                                                           | <u>Page</u> |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| A                | Memorandum from the Under Secretary of Defense for Research and Engineering, 16 August 1983, Subject: Mandatory Use of Military Telecommunications Standards in the MIL-STD-188 Series | 39          |

| B                | List of Abbreviations and Acronyms used in MIL-STD-188-114A                                                                                                                            | 41          |

| C                | Guidelines on Interconnections                                                                                                                                                         | 43          |

| <u>Paragraph</u> | <u>Title</u>                                                                                                                                                                           | <u>Page</u> |

| 30               | GENERAL                                                                                                                                                                                | 43          |

| 30.1             | Scope                                                                                                                                                                                  | 43          |

| 30.2             | Application                                                                                                                                                                            | 43          |

| 30.3             | Guidelines on interconnecting wire or cable characteristics                                                                                                                            | 43          |

| 30.3.1           | Conductor size                                                                                                                                                                         | 43          |

| 30.3.2           | Mutual pair capacitance                                                                                                                                                                | 44          |

| 30.3.3           | Stray capacitance                                                                                                                                                                      | 44          |

| 30.3.4           | Pair-to-pair balanced crosstalk                                                                                                                                                        | 44          |

| 30.3.5           | Wire or cable length for unbalanced voltage digital interface circuit                                                                                                                  | 44          |

| 30.3.6           | Wire or cable length for balanced voltage digital interface circuit                                                                                                                    | 46          |

| 30.4             | Wire or cable termination resistance                                                                                                                                                   | 49          |

| 30.5             | Fail safe operation                                                                                                                                                                    | 49          |

| 30.5.1           | Example of fail safe operation for unbalanced voltage digital interface circuit                                                                                                        | 50          |

| 30.5.2           | Example of fail safe operation for balanced voltage digital interface circuit                                                                                                          | 50          |

| 30.6             | Optional grounding arrangements                                                                                                                                                        | 53          |

| 30.6.1           | Signal common return for unbalanced voltage digital interface circuit                                                                                                                  | 55          |

| <u>Appendix</u>  |                                                                                                                                                                                        |             |

| D                | Guidelines on Interoperation Among Devices Complying with Different Low Level Digital Interface Standards                                                                              | 57          |

MIL-STD-188-114A

30 September 1985

| <u>Paragraph</u> | <u>Title</u>                                                                                 | <u>Page</u> |

|------------------|----------------------------------------------------------------------------------------------|-------------|

| 40               | GENERAL                                                                                      | 57          |

| 40.1             | Scope                                                                                        | 57          |

| 40.2             | Application                                                                                  | 57          |

| 40.3             | Unbalanced voltage digital<br>interface standards                                            | 57          |

| 40.4             | Balanced voltage digital<br>interface standards                                              | 57          |

| 40.5             | Interfacing balanced or<br>unbalanced generators with<br>balanced or unbalanced receivers    | 58          |

| 40.5.1           | Examples of interfacing<br>unbalanced generators with<br>balanced or unbalanced<br>receivers | 59          |

| 40.5.2           | Examples of interfacing<br>balanced generators with<br>balanced or unbalanced<br>receivers   | 59          |

MIL-STD-188-114A

30 September 1985

## 1. SCOPE

1.1 Purpose. This document specifies the electrical characteristics of the unbalanced voltage and the balanced voltage digital interface circuits, normally implemented in integrated circuit (IC) technology. These circuits shall be employed for the interchange of serial digital binary signals between and among Data Terminal Equipment (DTE) and Data Circuit Terminating Equipment (DCE) or in any interconnection of binary signals between physically separated equipment, regardless of the type of information, such as digitized voice or data, that is represented by the binary signals.

The technical parameters promulgated by this document represent, in general, minimum interoperability and performance characteristics which may be exceeded in order to satisfy specific requirements. Additional nonstandard interface characteristics may also be implemented to satisfy specific interoperability requirements, provided that a basic capability exists to interoperate with a standard interface as stated in this document.

This document does not specify other characteristics of the DTE/DCE interface, such as signal quality, and clock/data phase relationship, essential for satisfactory operation of the interconnected equipment. Those standards are contained in MIL-STD-188-100 and MIL-STD-188-200.

1.2 Application. This document shall be used in the design, installation, and operation of new communications facilities for both the long haul and tactical systems. This document shall be applicable to data, timing or clock, and control circuits employed at the interface between equipment where the information being conveyed is in the form of binary signals at the direct current (dc) baseband level. This document shall also be applicable to alarm and control circuits that are not directly related to data or timing.

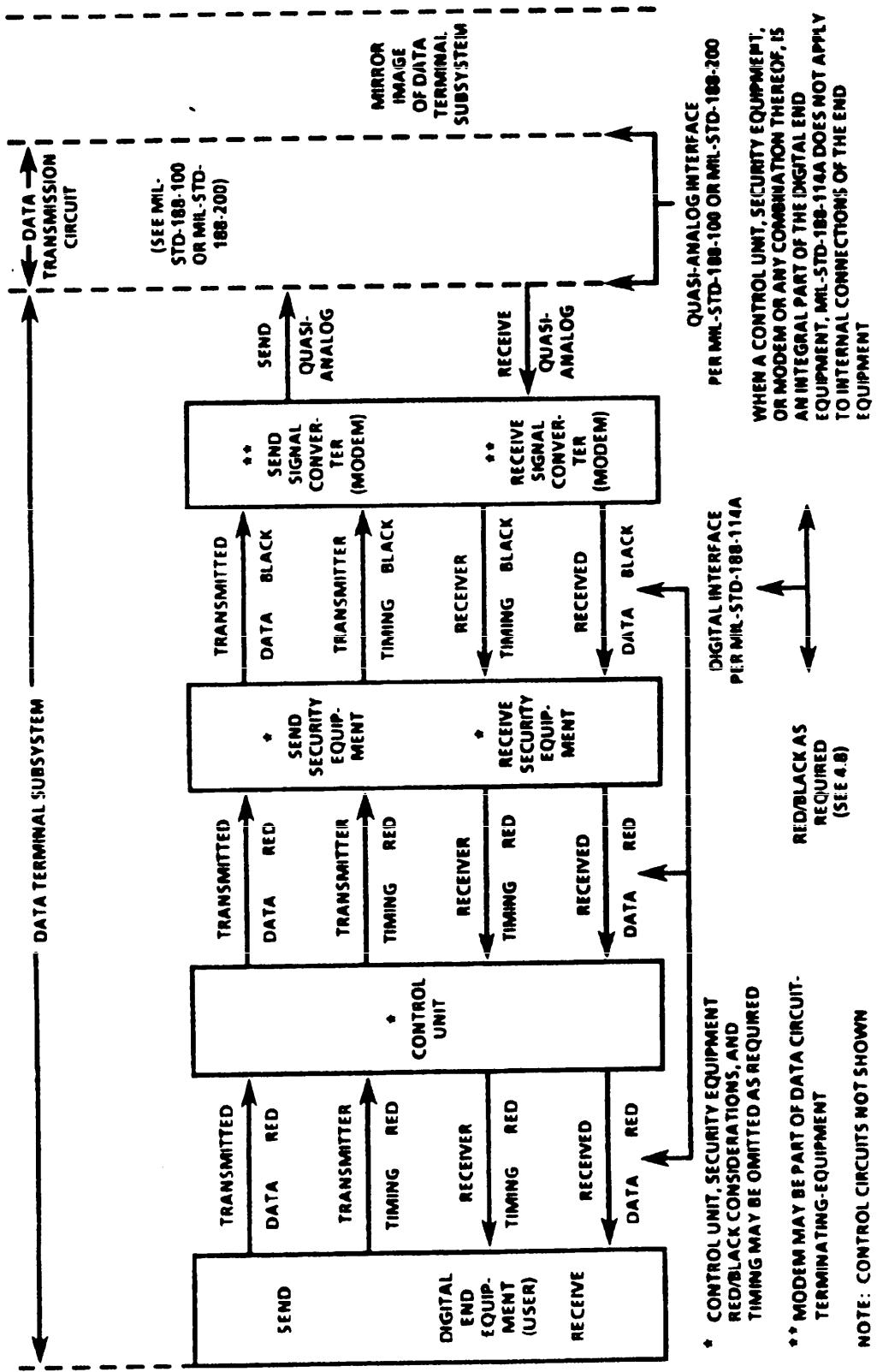

This document shall apply to teletypewriters, data terminals, the dc side of signal conversion equipment, both terminal and line side of cryptographic or cryptographic control equipment, digitized voice equipment, and remotely operated equipment where the interface is at the dc baseband. This document shall be applicable at all signaling rates regardless of the type of transmission medium used, e.g., a nominal 4 kilohertz (kHz) channel derived by frequency division multiplexing (FDM), a nominal 48 kHz channel derived by FDM, a channel derived by time division multiplexing (TDM), or a fiber optic or metallic wire connection. Figure 1 depicts a block diagram of a data terminal subsystem as an example to illustrate where the digital interface applies. Figure 1 shows data and timing circuits but does not show control circuits.

Any or all of the equipment of the terminal subsystem may be integrated and combined in a single piece of equipment. When combined in a single piece of equipment, this document does not apply to internal equipment connections.

Information on the interrelationship of this document with FED-STD-1020A, FED-STD-1030A and other low level digital interface standards is given in Appendix D.

MIL-STD-188-114A

30 September 1985

FIGURE 1. Block diagram of data terminal subsystem.

MIL-STD-188-114A

30 September 1985

This document does not apply to digital transmission subsystems employing specialized non-binary waveforms for transmission. Standards for these types of subsystems are under consideration and will be published in another document of the MIL-STD-188 series.

It is not intended that existing equipment and facilities be immediately converted to comply with the requirements of this document. New systems and those systems undergoing major modification or rehabilitation shall comply with the standards contained in this document subject to the applicable requirements of current procurement regulations.

1.3 System standards and design objectives. The parameters and other requirements specified in this document are mandatory system standards (see Appendix A) if the word "shall" is used in connection with the parameter value or requirement under consideration. Nonmandatory design objectives are indicated by parentheses after a standardized parameter value or by the word "should" in connection with the parameter value or requirement under consideration. For a definition of the terms "System Standard" and "Design Objective" see Federal Standard (FED-STD) 1037.

MIL-STD-188-114A

30 September 1985

2. REFERENCED DOCUMENTS

2.1 Government documents.

2.1.1 Standards. Unless otherwise specified, the following standards of the issue of the Department of Defense Index of Specifications and Standards (DoDISS) specified in the solicitation form a part of this standard to the extent specified herein.

STANDARDS

FEDERAL

FED-STD-1037      Glossary of Telecommunication Terms

MILITARY

MIL-STD-188-100      Common Long Haul and Tactical Communication System Technical Standards

MIL-STD-188-124      Grounding, Bonding and Shielding for Common Long Haul/Tactical Communication Systems

MIL-STD-188-200      System Design and Engineering Standards for Tactical Communications

2.1.2 Other Government documents and publications. The following other Government documents and publications form a part of this standard to the extent specified herein.

NACSIM 5100, Compromising Emanations Laboratory Test Requirements, Electromagnetics (U)

Quadripartite Standardization Agreement (QSTAG)

QSTAG-594      Electrical Characteristics of Digital Interface Circuits

(Copies of specifications, standards, handbooks, drawings, and publications required by contractors in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting officer.)

2.2 Order of precedence. In the event of a conflict between the text of this standard and the references cited herein, the text of this standard shall take precedence.

MIL-STD-188-114A

30 September 1985

3. DEFINITIONS

3.1 Definitions. Definition of terms used in this document shall be as specified in FED-STD-1037.

3.2 Abbreviations and acronyms. Abbreviations and acronyms used in this document are listed in Appendix B.

MIL-STD-188-114A

30 September 1985

#### 4. GENERAL REQUIREMENTS

**4.1 Description of digital interface circuits.** The interface circuits consist of a generator connected by an interconnecting wire or cable to a load. The load is comprised of one or more receivers and a termination resistor, where applicable. The electrical characteristics of the digital interface circuits are specified in terms of required voltage, current and resistance values obtained from direct measurement of the generator and receiver components. The generator characteristics for the unbalanced voltage digital interface circuit are electrically different from the generator characteristics for the balanced voltage digital interface circuits, whereas the receiver characteristics are electrically identical for both the unbalanced and the balanced voltage digital interface circuits. Guidance is given in Appendix C concerning the characteristics of the interconnecting wire or cable and with respect to limitations on signaling rates imposed by the parameters of wire or cable length, balance, termination, and generation of near-end crosstalk, where applicable. Information on the interrelation of this document with other low level digital interface standards is given in Appendix D. The requirements for signal waveshaping, generally necessary to reduce unbalanced circuit near-end crosstalk to adjacent circuits, are also described. For the purpose of this document, the terms interface circuit and interchange circuit are considered to be identical.

**4.2 Description of functional interchange circuits.** Functional interchange circuits are used to connect DTE and DCE for the purpose of exchanging data and timing signals and to control the flow of information. Flow control may be extended from one DTE through one or more DCE to another DTE on an end-to-end basis by appropriate communications protocols. Functional interchange circuits may be subdivided into four general classes:

- Data (send and receive)

- Timing or clock (send and receive)

- Control (including status, indicator and alarm),

- Ground or common return.

Connectors, pin assignments and communications protocols are not standardized in this document.

**4.3 Signaling rate range.** The unbalanced voltage digital interface circuit (see 5.1) can generally be utilized on data, timing or clock, and control circuits where the signaling rate on these circuits is up to 100 kilobits per second (kb/s). The balanced voltage digital interface circuit (see 5.2) can generally be utilized on data, timing or clock, and control circuits where the signaling rate on these circuits is up to 10 megabits per second (Mb/s). The terminated voltage digital interface circuit (see 5.3) can generally be utilized on data, timing or clock, and control circuits where the signaling rate on these circuits exceeds 10 Mb/s.

MIL-STD-188-114A

30 September 1985

Digital interface devices meeting the electrical characteristics of this document need not operate over the entire signaling rate range indicated above. The devices may be designed to operate over narrower ranges to more economically satisfy specific applications, particularly at the lower signaling rates.

**4.4 Selection of type of digital interface circuit.** The choice of either the balanced or the unbalanced voltage digital interface circuit is left to the designer and depends upon the signaling rate, the distance between generator and load, noise and grounding conditions, and other factors.

**4.4.1 Types of balanced generators.** Three different types of generators may be used for the balanced voltage digital interface circuit. All three types of balanced generators use the same type of receiver used with unbalanced generators. The three types of balanced generators are as follows:

The type I generator has an offset voltage of not more than 0.4 volts and is intended to be used for balanced interfaces operating at signaling rates below 100 kb/s. The low offset voltage is necessary for interoperability with older military digital equipment. (See 4.5.) The type I generator corresponds to the original MIL-STD-188-114 balanced generator.

The type II generator has an offset voltage of up to three volts and corresponds to the FED-STD-1020A and EIA RS-422A balanced generators. The type II generator is intended to be used for balanced interfaces operating at signaling rates between 100 kb/s and 10 Mb/s where no interoperability requirements with older military digital equipment is expected to exist.

The type III generator is a new terminated voltage generator and is intended to be used for balanced voltage digital interface circuits operating at signaling rates over 10 Mb/s.

**4.4.2 Use of balanced voltage digital interface circuit.** While the balanced voltage digital interface circuit is intended for use at higher signaling rates than the unbalanced voltage digital interface circuit, the general use of the balanced voltage digital interface circuit is recommended where any of the following conditions prevail:

- a. The interconnecting wire or cable is too long for effective unbalanced operation.

- b. The interconnecting wire or cable is exposed to extraneous noise sources that may cause an unwanted voltage in excess of plus or minus one volt measured differentially between the signal conductor and circuit common ground at the load end of the wire or cable with a 50-ohm resistor substituted for the generator.

- c. It is necessary to minimize interference with other signals.

MIL-STD-188-114A

30 September 1985

d. Inversion of signal sense of the transmitted signal may be required, e.g., plus MARK to minus MARK may be obtained by inverting the wire or cable pair of the balanced generator. (See Figure 29.)

**4.4.3 Use of balanced and unbalanced voltage digital interface circuits.** The parameter values for the generator and load components of the interface are designed such that balanced and unbalanced voltage digital interface circuit connections may be carried in the same cable. For example, the balanced voltage digital interface circuits may be used for data and timing while the unbalanced voltage digital interface circuits may be used for control functions operating with lower signaling rates than the data and timing circuits.

**4.5 Relationship with other digital interface standards.** The parameter values contained in this document are identical to corresponding parameter values of FED-STD-1020A and FED-STD-1030A with the exception of the balanced generator offset voltage  $V_{os}$  (see 5.2.1.4) of the type I generator.

This deviation is considered essential for interfaces operating at signaling rates below 100 kb/s, in order to ensure compatibility and direct interoperability between new equipment designed in accordance with this document and equipment currently in the inventory designed in accordance with previous standards of the MIL-STD-188 series. The term "direct interoperability" should be understood to mean that no modification of low level digital interface equipment is required and no additional device is needed for satisfactory exchange of information between older and new low level digital interface equipment.

The type II generators are intended for interfaces operating at signaling rates between 100 kb/s and 10 Mb/s, which are not expected to interface with older equipment designed in accordance with previous standards of the MIL-STD-188 series. The 0.4 volts offset voltage specified in this document for the type I generator is a more stringent subset and falls completely within the specifications of FED-STD-1020A.

**4.6 Grounding requirements.** Grounding of digital interface circuits shall comply with the applicable requirements of the current edition of MIL-STD-188-124.

NOTE: Optional grounding arrangements are contained in 30.6 of Appendix C.

**4.7 Interoperability requirements of ABCA Armies.** The electrical characteristics for binary signals at an interface for the exchange of digital information among American, British, Canadian and Australian (ABCA) Armies or Forces shall comply with the applicable requirements of the current edition of QSTAG 594.

NOTE: The requirements of this document are compatible with the requirements

MIL-STD-188-114A

30 September 1985

4.8 Compromising emanations (TEMPEST) requirements. Digital interface circuits requiring TEMPEST protection shall comply with the applicable requirements of the current edition of the NACSIM 5100 series.

MIL-STD-188-114A

30 September 1985

## 5. DETAILED REQUIREMENTS

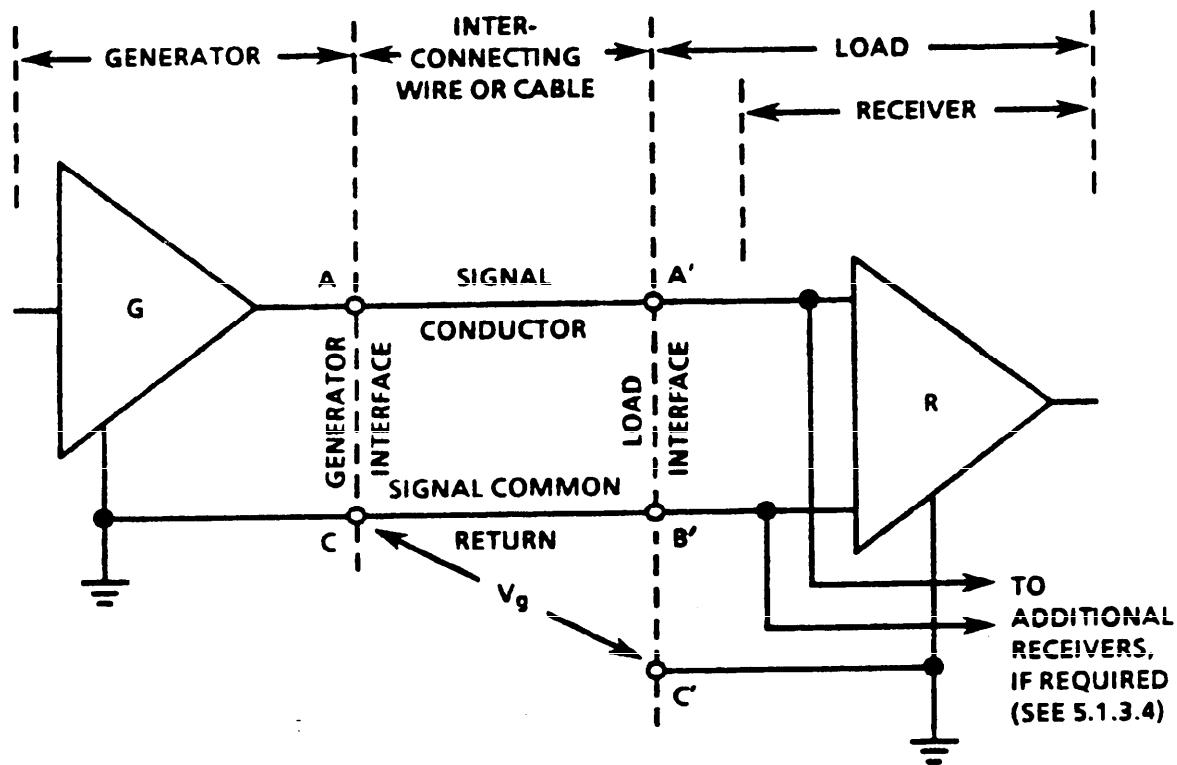

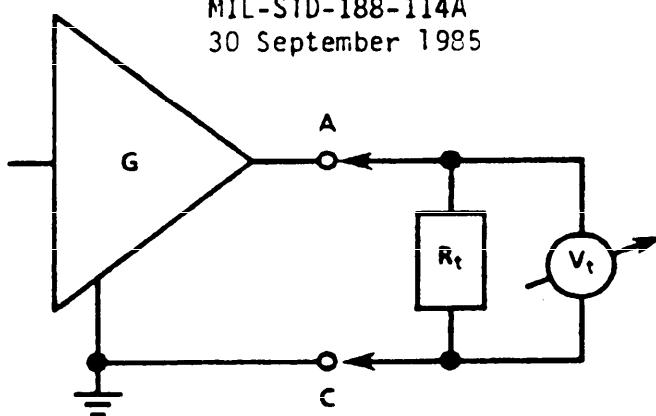

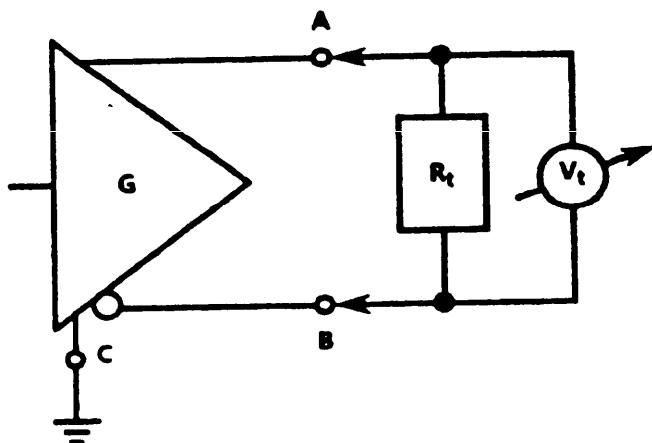

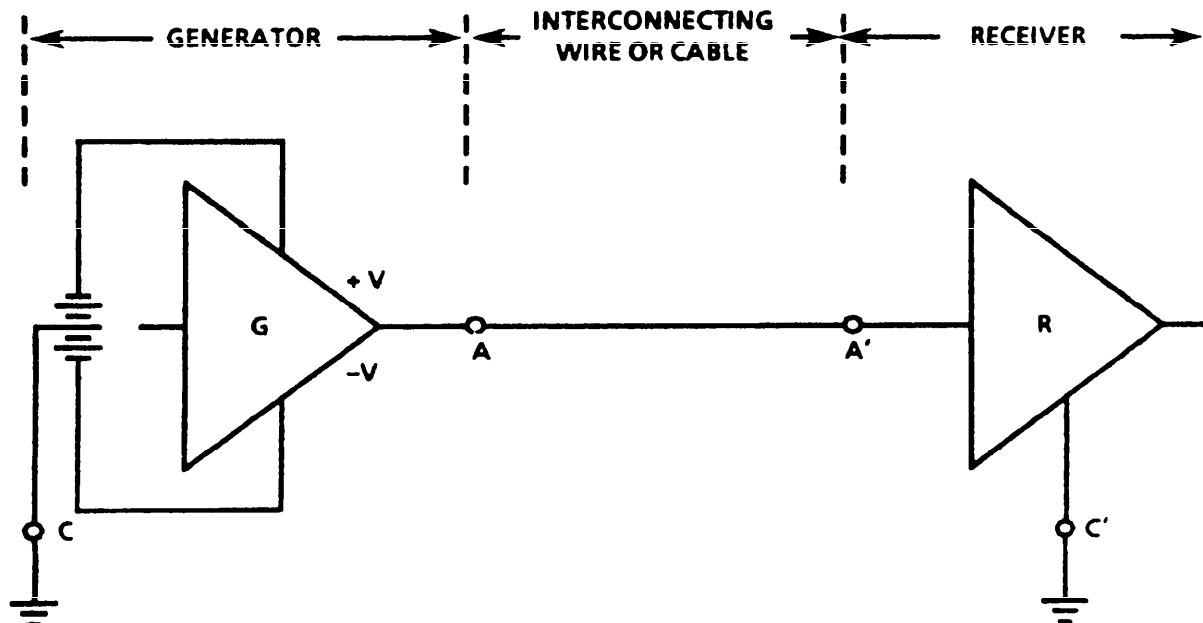

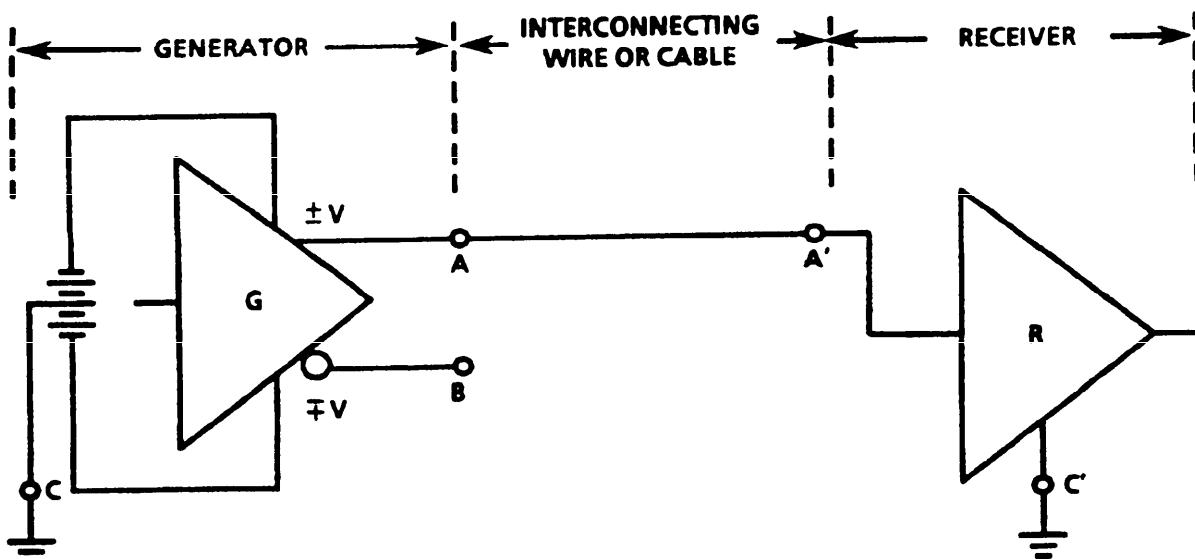

5.1 Unbalanced voltage digital interface circuit. The unbalanced voltage digital interface circuit is shown in Figure 2. The circuit consists of three parts: the generator (G), the interconnecting wire or cable, and the load. The load consists of one or more receivers (R) (see 5.1.3.4). The electrical characteristics of the generator and the receiver are specified in terms of direct electrical measurements. Guidance is provided in 30.3 of Appendix C regarding the electrical and physical characteristics of the interconnecting wire or cable.

### LEGEND:

- A, C - GENERATOR INTERFACE POINTS

- C - GENERATOR CIRCUIT GROUND

- A', B' - LOAD INTERFACE POINTS

- C' - LOAD CIRCUIT GROUND

- $V_g$  - GROUND POTENTIAL DIFFERENCE

FIGURE 2. Unbalanced voltage digital interface circuit.

MIL-STD-188-114A

30 September 1985

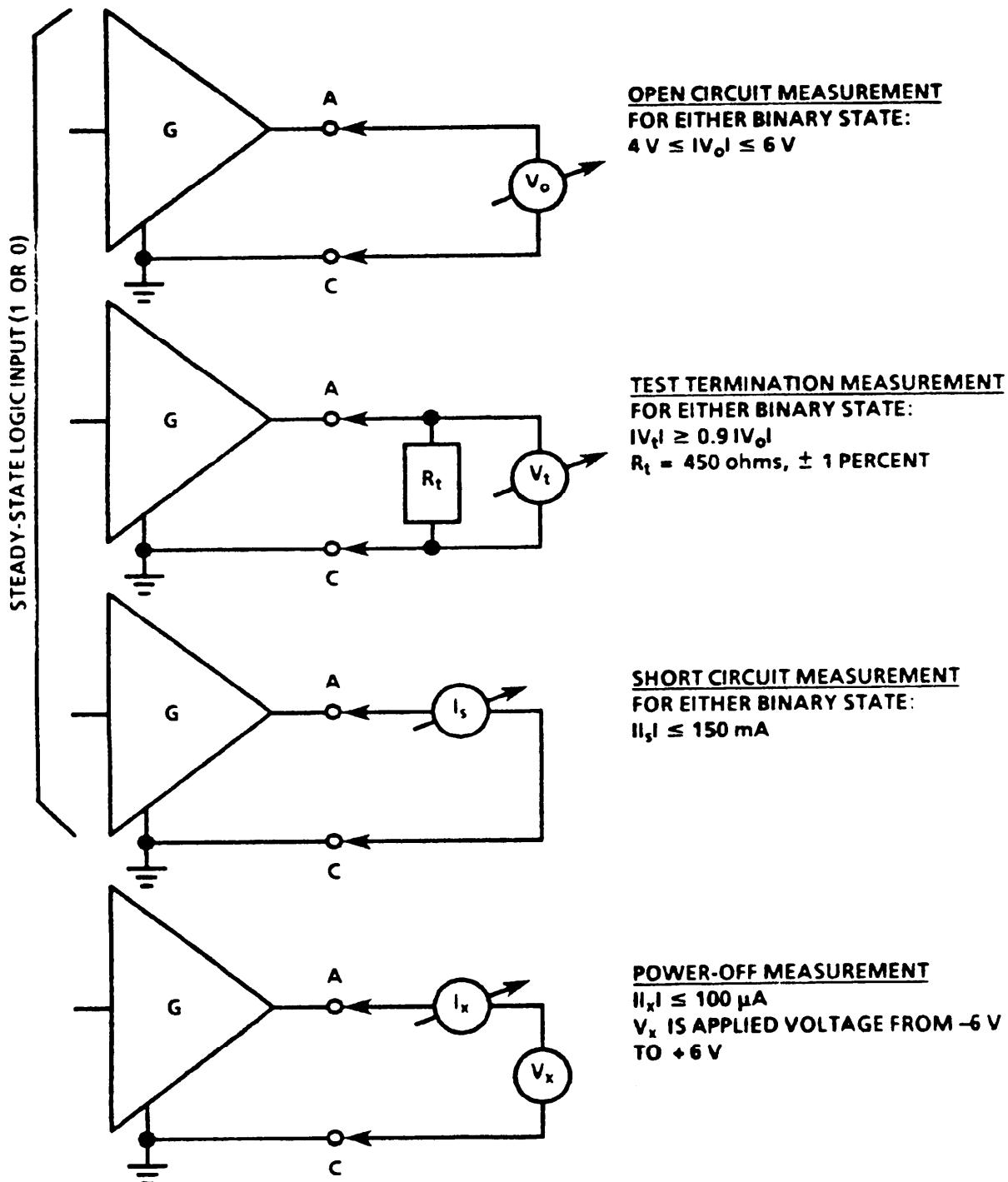

5.1.1 Generator characteristics. The electrical characteristics of the unbalanced generator are specified in accordance with measurements illustrated in Figures 3 through 6 and described in 5.1.1.1 through 5.1.1.9. The measurements are under static conditions, whereas measurements under dynamic conditions are not standardized. A generator meeting these requirements results in a low impedance (50 ohms or less) unbalanced voltage source that will produce a voltage applied to the interconnecting wire or cable in the range of 4 volts to 6 volts.

5.1.1.1 Signal sense. The signal sense of the generator output voltages appearing across the interconnecting wire or cable (see Figure 2) shall be as shown in Table I.

TABLE I. Signal sense for unbalanced generators.

| VOLTAGE POLARITY<br>(See Figure 2)       | DATA       | TIMING          | CONTROL and ALARM |

|------------------------------------------|------------|-----------------|-------------------|

| Point A negative with respect to point C | 1 or MARK  | OFF (QUIESCENT) | OFF               |

| Point A positive with respect to point C | 0 or SPACE | ON (ACTIVE)     | ON                |

NOTE: The MARK and SPACE states for telegraphy and data transmission have been changed from positive MARK and negative SPACE (MIL-STD-188-100, subparagraph 4.3.1.5) to negative MARK and positive SPACE. It is not intended that existing equipment and facilities be converted to the negative MARK/positive SPACE states unless a major facility modification or rehabilitation is planned and such conversion could be accommodated during that work. It is, however, intended that new procurement of equipment and facilities will insure that a provision for negative and positive MARK is accommodated. This does not mean that negative MARK will necessarily be implemented immediately simply because the equipment or facility is new. This guidance is only intended to mean that new equipment or facilities will be purchased with the positive and negative MARK capability and the facilities engineering or operating agency will be expected to make the necessary decisions to change to negative MARK on a case by case basis, subject to operational and fiscal constraints.

5.1.1.2 Signaling rate range. Not standardized. (See Appendix C)

5.1.1.3 Open-circuit measurement. (See Figure 3.) For either binary state, the magnitude of the voltage ( $V_o$ ) measured between the generator output terminal A and generator circuit ground (terminal C) shall not be less than 4 volts nor more than 6 volts. For the opposite binary state, the polarity of  $V_o$  shall be reversed ( $\bar{V}_o$ ).

MIL-STD-188-114A

30 September 1985

FIGURE 3. Unbalanced generator parameter measurements.

MIL-STD-188-114A

30 September 1985

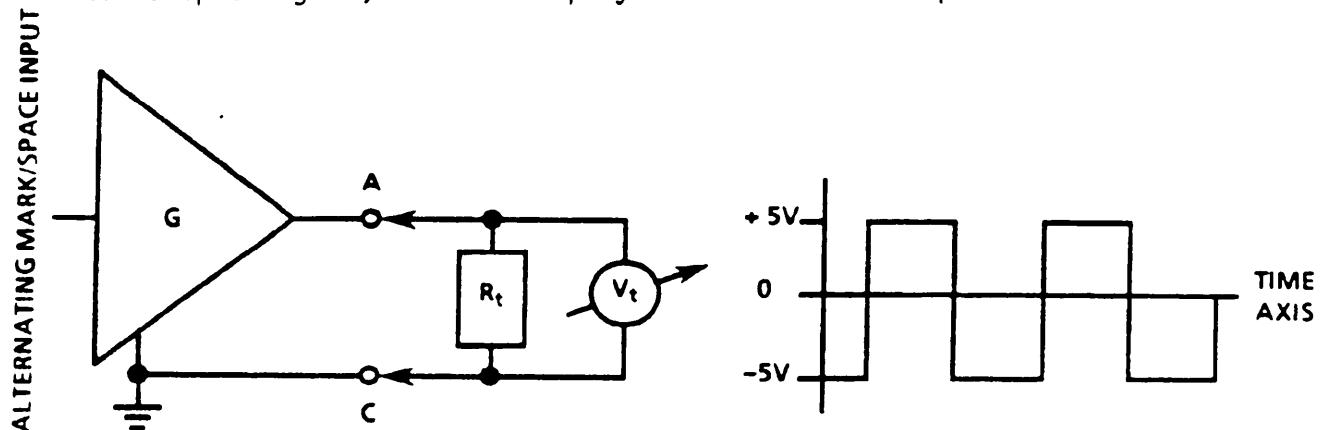

5.1.1.4 Test termination measurement. (See Figure 3.) With a test load of 450 ohms  $\pm 1$  percent connected between the generator output terminal A and generator circuit ground (terminal C), the magnitude of the voltage ( $V_t$ ) measured between the generator output terminal A and generator circuit ground (terminal C) shall not be less than 90 percent of the magnitude of  $V_c$  for one binary state. For the opposite binary state, the polarity of  $V_t$  shall be reversed ( $V_t$ ) and  $V_t$  shall not be less than 90 percent of the magnitude of  $V_o$ .

NOTE: A nominal voltage waveform for alternating binary states is shown in Figure 4. This waveform is intended to represent a typical unbalanced generator output signal, such as displayed on an oscilloscope.

LEGEND:  $V_t = 5$  V (ASSUMED VALUE)

$R_t = 450$  ohms

FIGURE 4. Nominal waveform of unbalanced generator.

5.1.1.5 Short-circuit measurement. (See Figure 3.) With the generator output terminal A short-circuited to generator circuit ground (terminal C), the magnitude of the current  $I_s$  flowing through the generator output terminal A shall not exceed 150 milliamperes (mA) for either binary state.

5.1.1.6 Power-off measurement. (See Figure 3.) Under power-off conditions, the magnitude of the generator output leakage current ( $I_x$ ), with a voltage  $V_x$  ranging between +6 volts and -6 volts applied between the generator output terminal A and generator circuit ground (terminal C), shall not exceed 100 microamperes.

MIL-STD-188-114A

30 September 1985

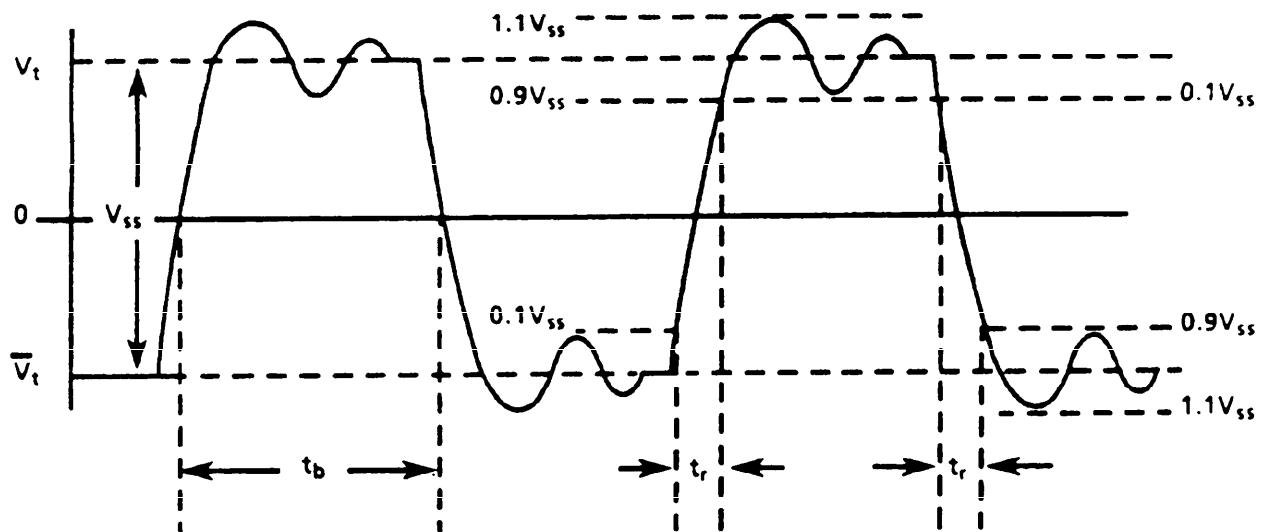

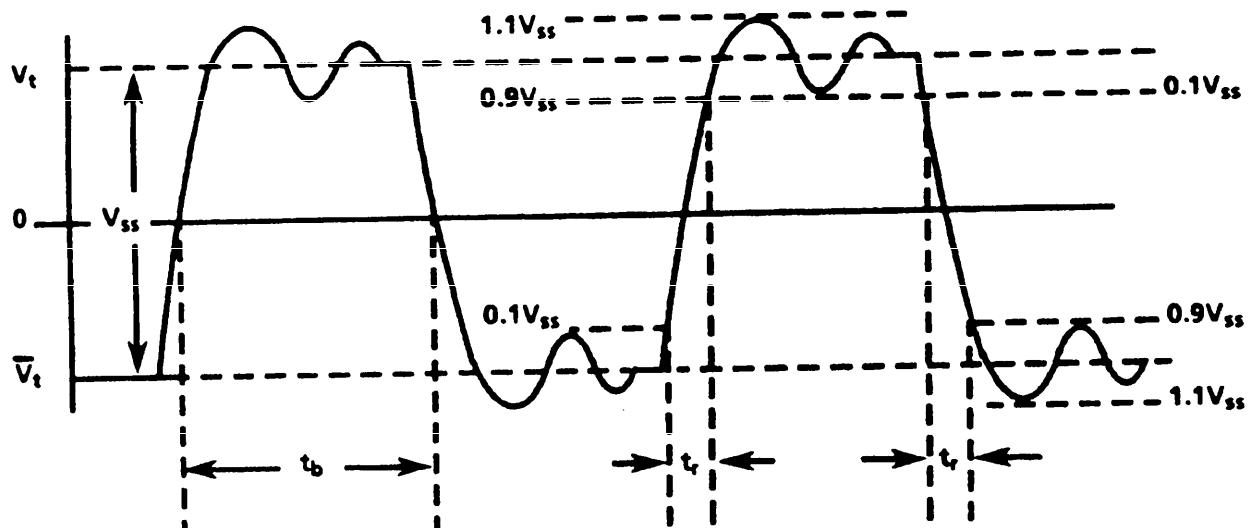

5.1.1.7 Output signal waveform. (See Figure 5.) During transitions of the generator output between alternating binary states (one-zero-one-zero, etc.), the signal measured across a 450 ohms  $\pm 1$  percent test load connected between the generator output terminal A and generator circuit ground (terminal C) shall be such that the voltage monotonically changes between 0.1 and 0.9 of  $V_{ss}$ . Thereafter, the signal voltage shall not vary more than 10 percent of  $V_{ss}$  from the steady state value, until the next binary transition occurs, and at no time shall the instantaneous magnitude of  $V_t$  or  $\bar{V}_t$  exceed 6 volts, nor be less than 3.6 volts.  $V_{ss}$  is defined as the voltage difference between the two terminated steady state values  $V_t$  and  $\bar{V}_t$  of the generator output.

5.1.1.8 Output signal waveshaping. (See Figure 5.) Waveshaping of the generator output signal shall be employed to control the level of interference (near-end crosstalk) that may be coupled to adjacent circuits in an interconnection. The rise time  $t_r$  of the signal shall be controlled to ensure that the signal reaches 0.9  $V_{ss}$  between 0.1 and 0.3 of the unit interval ( $t_b$ ) at the maximum signaling rate. Below 1 kb/s,  $t_r$  shall be between 100 microseconds and 300 microseconds. The method of providing the waveshaping is not standardized, but examples are given in Note 3, below.

NOTE 1: The near-end crosstalk is a function of both rise time and wire or cable length (see 30.3.5 of Appendix C) and, therefore, in establishing the standard for waveshaping, both of these characteristics have been considered.

NOTE 2: If a generator is to operate over a range of signaling rates and employs a fixed amount of waveshaping which meets the standard for the maximum signaling rate of the operating range, the waveshaping is considered adequate for all lesser signaling rates and equal or lesser cable lengths recommended for the maximum signaling rate in Figure 18 of Appendix C, even though this may result in a rise time less than 0.1  $t_b$  for the actual operating rate.

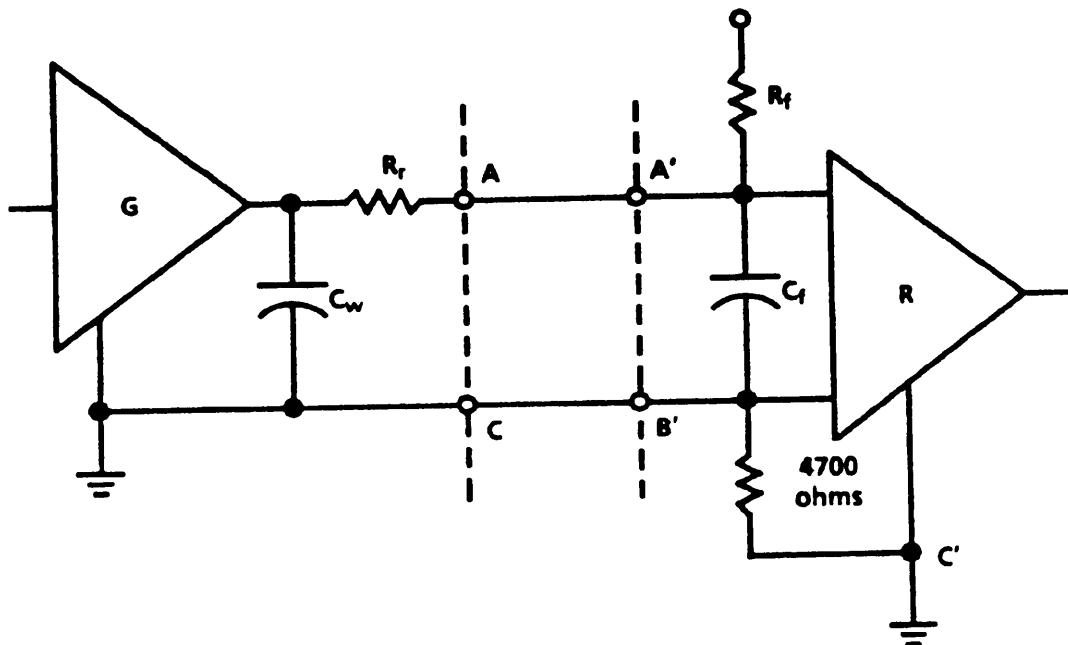

NOTE 3: The required waveshaping may be accomplished, for example, either by providing a slew rate control in the generator or by inserting an RC filter at the generator interface point. A combination of these methods may also be employed. Care should be taken to prevent oscillations which may be caused by slew rate control circuitry. The designer is cautioned that the use of internal generator waveshaping controls provided by some manufacturers may give rise to instability during generator transitions. Measured results of this instability have revealed burst oscillations in the gigahertz (GHz) frequency range which can cause faulty equipment operation. For this reason, until a solution has been found, the preferred waveshaping technique is the external RC network. An example of the RC filter method is shown in Figure 6. Typical values of capacitance  $C_w$ , with the value of  $R_w$  selected so that  $R_w$  plus the output resistance of the generator is approximately 50 ohms, that

MIL-STD-188-114A

30 September 1985

LEGEND:  $R_t$  = 450 ohms  $\pm$  1 PERCENT

$|V_{ss}| = |V_t - \bar{V}_t|$

$V_{ss}$  = DIFFERENCE IN STEADY STATE VOLTAGES

$t_b$  = UNIT INTERVAL

$t_r$  = 100  $\mu$  TO 300  $\mu$ s WHEN  $t_b \geq 1$ ms

$t_f$  = 0.1  $t_b$  TO 0.3  $t_b$  WHEN  $t_b < 1$ ms

FIGURE 5. Unbalanced generator output signal waveform.

may be employed with typical twisted pair cable are also given. These values apply for operating distances from zero to that shown by the curve in Figure 18 of Appendix C for the applicable signaling rate. Where generators are driving clock leads, the same waveshaping design may be employed as used on the associated data leads. If the clock signaling rate is directly related to the data signaling rate, one half of the period of the clock should be used in lieu of  $t_b$  to determine rise time. (See also subparagraph 4.3.1.6 of MIL-STD-188-100 and subparagraph 5.3.6 of MIL-STD-188-200).

MIL-STD-188-114A

30 September 1985

**MAXIMUM SIGNALING**

| <u>RATE (kb/s)</u> | <u><math>C_w</math> (MICROFARADS)</u> |

|--------------------|---------------------------------------|

| 0 - 2.5            | 1.0                                   |

| 2.5 - 5            | 0.47                                  |

| 5 - 10             | 0.22                                  |

| 10 - 25            | 0.10                                  |

| 25 - 50            | 0.047                                 |

| 50 - 100           | 0.022                                 |

$R_w$  IS APPROXIMATELY

50 ohms MINUS THE

GENERATOR OUTPUT

RESISTANCE

**FIGURE 6. Example method for waveshaping of unbalanced voltage digital interface circuit.**

**5.1.1.9 High impedance output state.** The generator output should be permitted to assume a high impedance state, if required for multiple generator bus operation. If a high impedance state is implemented, the output voltage shall be nominally zero for the high impedance state when measured with a test termination as stated in 5.1.1.4.

**5.1.2 Wire or cable characteristics.** Not standardized.

**NOTE:** Guidelines on wire or cable characteristics are given in 30.3 of Appendix C.

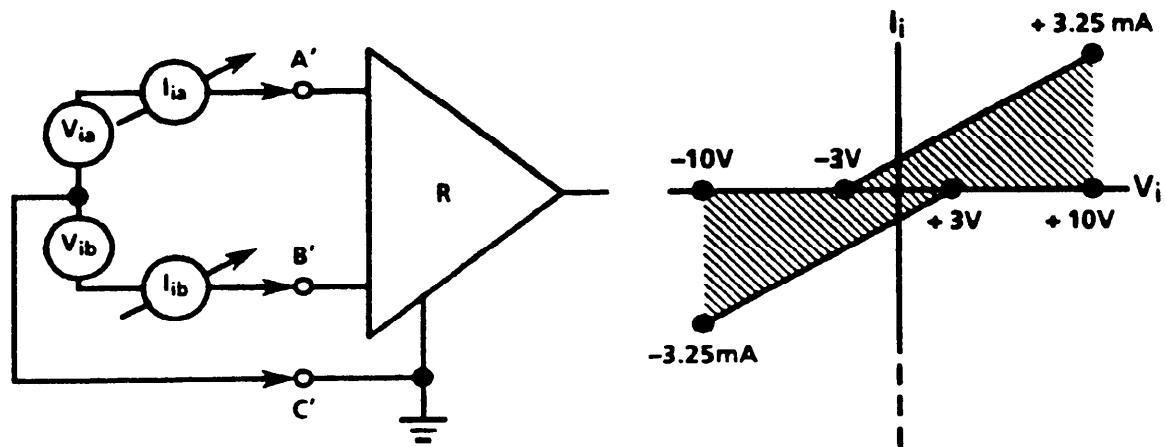

**5.1.3 Load characteristics.** The load consists of one or more receivers (R) as shown in Figure 2. The electrical characteristics of a single receiver without fail safe provision are specified in terms of the measurements illustrated in Figures 7 through 9 and described in 5.1.3.1 through 5.1.3.3. A device meeting these requirements results in a differential receiver having a high input impedance (4000 ohms or more), a small input threshold transition region between -0.2 volts and +0.2 volts, and allowance for an internal bias voltage not to exceed 3 volts in magnitude. Multiple receivers and a provision for fail safe operation for specific applications are allowed in the load within the limitations specified in 5.1.3.6. The receiver used in the load for the unbalanced voltage digital interface circuit is electrically identical to the receiver for the balanced voltage digital interface circuits stated in 5.2 and 5.3.

MIL-STD-188-114A

30 September 1985

5.1.3.1 Receiver input current-voltage measurement. (See Figure 7.) With the voltage  $V_{ia}$  (or  $V_{ib}$ ) ranging between -10 volts and +10 volts, while  $V_{ib}$  (or  $V_{ia}$ ) is held at 0 volts (grounded), the resultant input current  $I_{ia}$  (or  $I_{ib}$ ) shall remain within the shaded region shown in the graph in Figure 8. These measurements shall be made with the power supply (or supplies) of the receiver in both the power-on and power-off conditions.

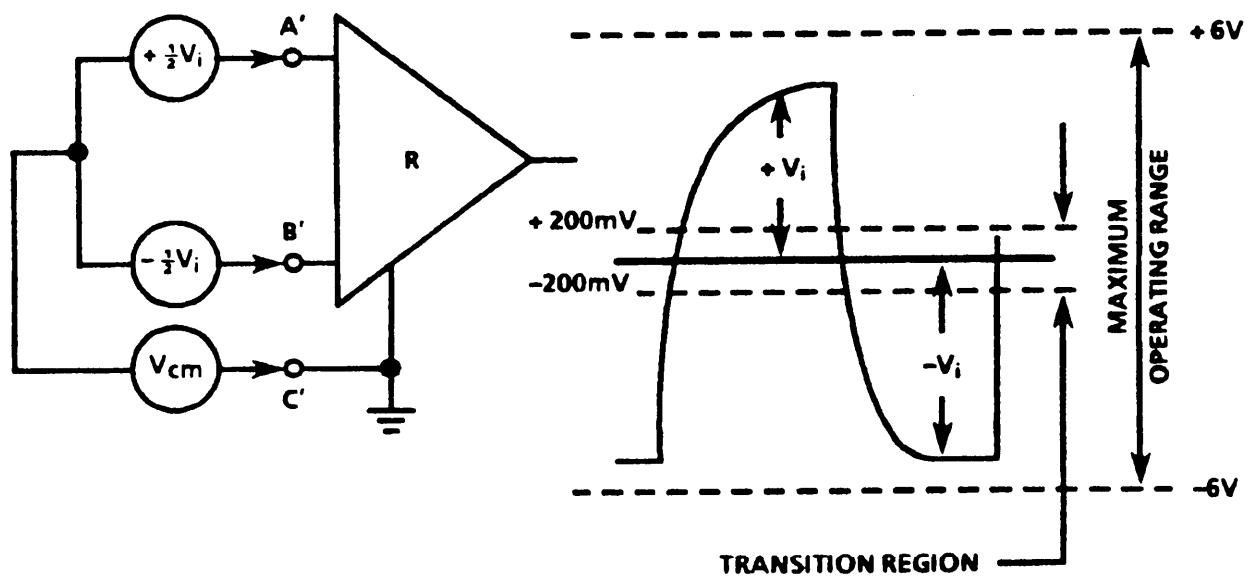

5.1.3.2 Receiver input sensitivity measurement. (See Figure 8.) Over an entire common mode voltage ( $V_{cm}$ ) range of -7 volts to +7 volts, the receiver shall require a differential input voltage  $V_i$  of not more than 200 millivolts (mV) to correctly assume the intended binary state. The common mode voltage  $V_{cm}$  is defined as the algebraic mean of the two voltages appearing at the receiver input terminals A' and B' with respect to the receiver circuit ground C'. Reversing the polarity of  $V_i$  shall cause the receiver to assume the opposite binary state. The receiver is required to maintain correct operation for differential input signal voltages ranging between 200 mV and 6 volts in magnitude. The maximum voltage (signal plus common mode) present between either receiver input terminal and receiver circuit ground shall not exceed 10 volts in magnitude and shall not cause the receiver to operationally fail. Additionally, the receiver shall tolerate the conditions specified in 5.1.5 without being damaged.

NOTE: Designers of terminating hardware should be aware that slow signal transitions with noise present may give rise to instability or oscillatory conditions in the receiver and, therefore, appropriate techniques should be implemented to prevent such behavior. For example, adequate hysteresis may be incorporated into the receiver to prevent such conditions.

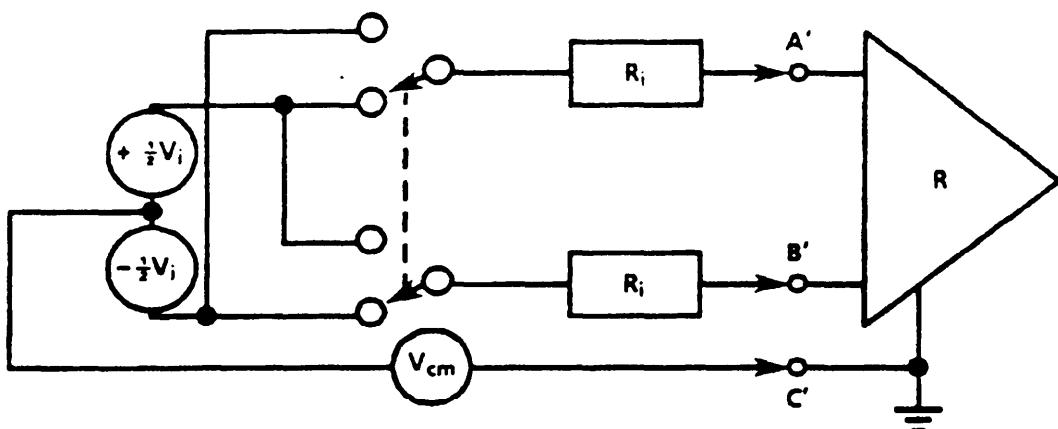

5.1.3.3 Receiver input balance measurement. (See Figure 9.) The balance of the receiver input voltage-current characteristics and bias voltages shall be such that the receiver will remain in the intended binary state when a differential voltage ( $V_i$ ) of 400 mV is applied through resistors of 500 ohms  $\pm 1$  percent to each input terminal A' and B', as shown in Figure 9, and  $V_{cm}$  is varied between -7 volts and +7 volts. When the polarity of  $V_i$  is reversed, the opposite binary state shall be maintained under the same conditions.

5.1.3.4 Multiple receivers. Not standardized.

NOTE: The use of up to ten receivers in the load may be optionally employed. However, extreme caution must be exercised to avoid performance degradation due to signal reflections from stub lines emanating from the load interface point to the receivers. See 5.1.3.6 for limits on total load resistance and sensitivity.

MIL-STD-188-114A

30 September 1985

FIGURE 7. Receiver input current-voltage measurement.

FIGURE 8. Receiver input sensitivity measurement.

MIL-STD-188-114A

30 September 1985

LEGEND:  $V_{cm} = -7 \text{ V TO } +7 \text{ V}$

$V_i = 400 \text{ mV}$

$R_i = 500 \text{ ohms, } \pm 1 \text{ PERCENT}$

FIGURE 9. Receiver input balance measurement.

5.1.3.5 Fail safe operation. Where a fail safe is required, a provision shall be incorporated in the load to provide a steady binary condition (either MARK or SPACE as required by the application) to protect against certain fault conditions.

NOTE: The method of providing fail safe is not standardized. An example of fail safe operation is given in 30.5.1 of Appendix C.

5.1.3.6 Total load characteristic limits. The total load including multiple receivers and fail safe provisions shall have a resistance greater than 400 ohms between its input points (terminals A' and B' of Figure 2) and shall require a differential input voltage of not more than 200 mV for all receivers to assume the intended binary state.

5.1.4 Operational constraints. An unbalanced voltage digital interface circuit conforming to 5.1 will perform satisfactorily at signaling rates up to 100 kb/s providing that the following operational constraints are simultaneously satisfied:

- The interconnecting wire or cable length is within that recommended for the applicable signaling rate indicated in 30.3.5 of Appendix C.

- The common mode voltage at the receiver is less than 4 volts (peak). The common mode voltage is defined to be any uncompensated combination of generator-receiver ground potential difference, the generator offset voltage ( $V_{os}$ ), and longitudinally coupled peak random noise voltage measured between the receiver circuit ground and the wire or cable with the generator ends of the wire or cable short-circuited to ground.

MIL-STD-188-114A

30 September 1985

c. The amplitude of the received signal is at least 0.2 volts greater than the total peak noise between the signal conductor and common return at the load interface point, with a 50-ohm resistor substituted for the generator (and waveshaping network, if used) at the generator interface point.

NOTE: Care should be taken when power for distant receivers is supplied in the same or in adjacent conductors as used for data, clock or control signals, in order to avoid performance degradation that may be caused by power supply surges and spurious voltage transients.

5.1.5 Circuit protection. Interface circuit protection shall be provided such that any generator or receiver, under either the power-on or the power-off condition, shall not be damaged by occurrence of any of the following conditions:

- a. Voltage magnitudes of 12 volts (Design Objective: 25 volts) on the receiver leads.

- b. Shorting of the generator or the receiver terminals to ground or to each other.

- c. Crossing of the leads with any other physical leads of the interface circuit.

- d. Opening of either or both of the generator or receiver leads.

- e. Whenever the generator or receiver is to be connected by a metallic circuit directly to pairs of an outside plant cable, additional protective circuitry shall be provided to protect the generator and receiver against the spurious voltage transients and power surges commonly experienced across a cable pair or between either conductor of a cable pair and ground. The protective circuitry shall be adequate to ensure that the generator or receiver will not be damaged by the appearance across the cable pair or between either conductor and ground, of

- (1) a voltage transient of up to 1000 volts peak with a 5 microsecond rise time and decaying to 50 percent of peak voltage in 600 microseconds, and

- (2) a voltage transient of up to 350 volts peak with a 10 microsecond rise time and decaying to 50 percent of peak voltage in 2000 microseconds.

NOTE: The faults or conditions listed in 5.1.5 may cause the power dissipation in the interface devices to approach the maximum power dissipation that may be tolerated by a typical IC package. It is therefore cautioned that where multiple generators or receivers are implemented in a single IC package, only one such fault or condition per package may be tolerated at one time without damage occurring to the IC package.

MIL-STD-188-114A

30 September 1985

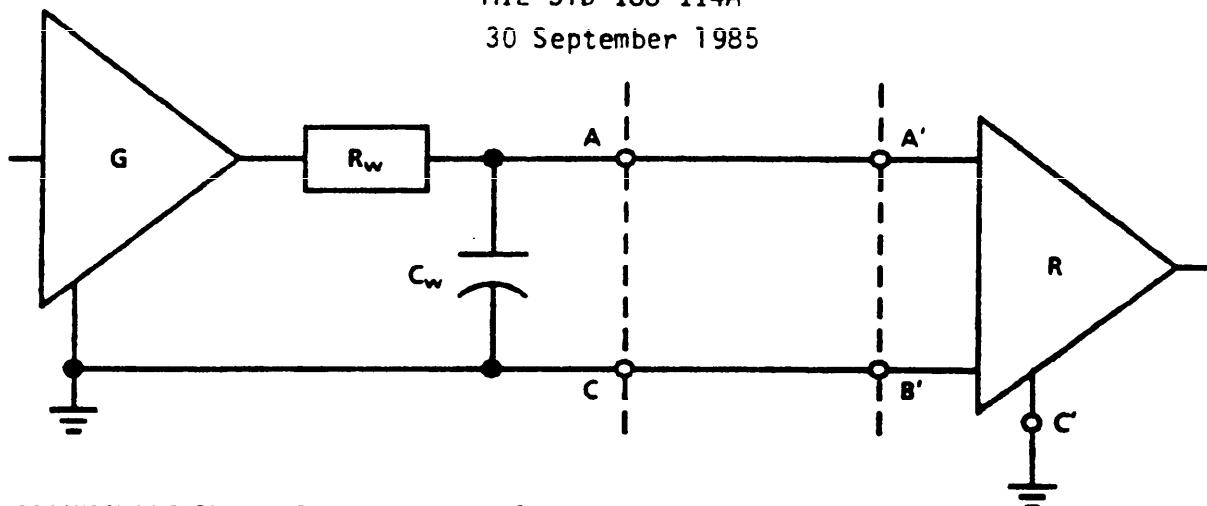

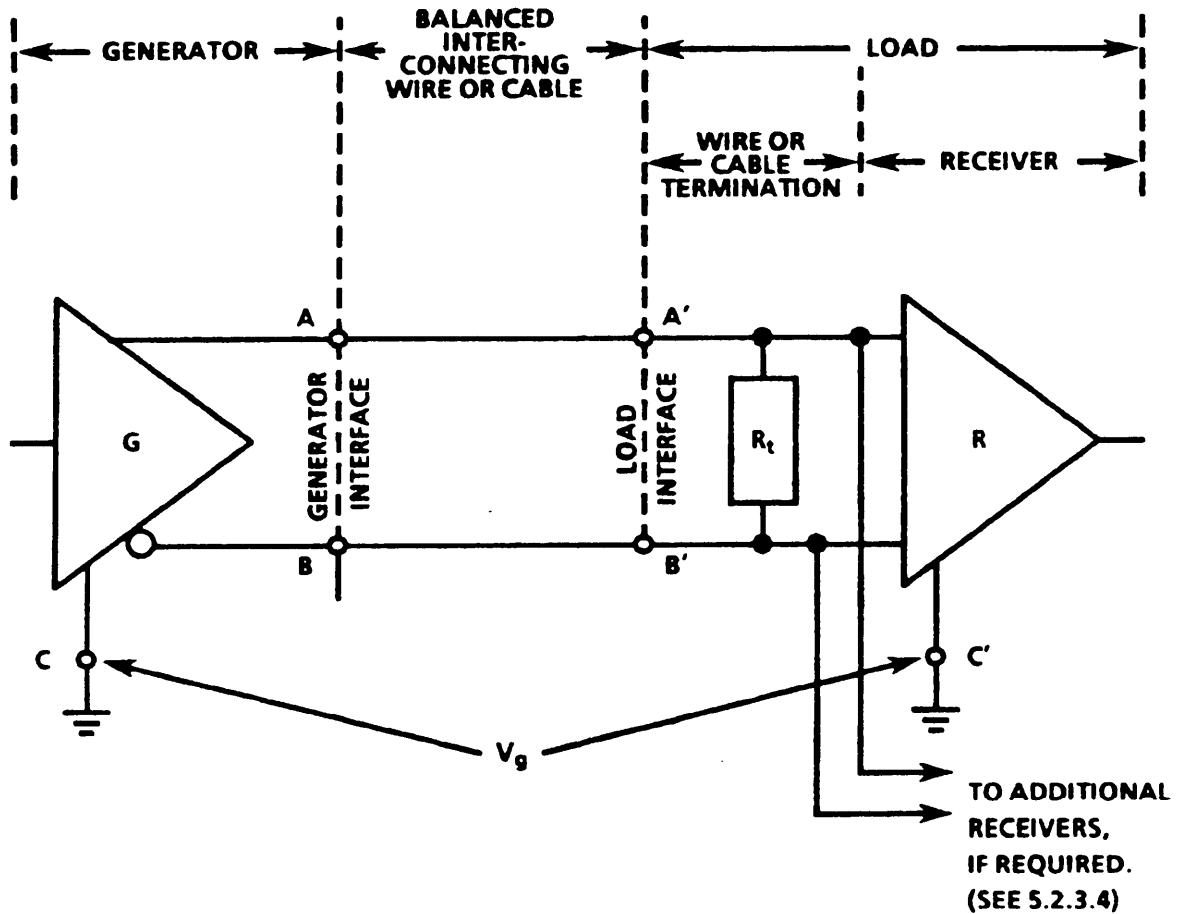

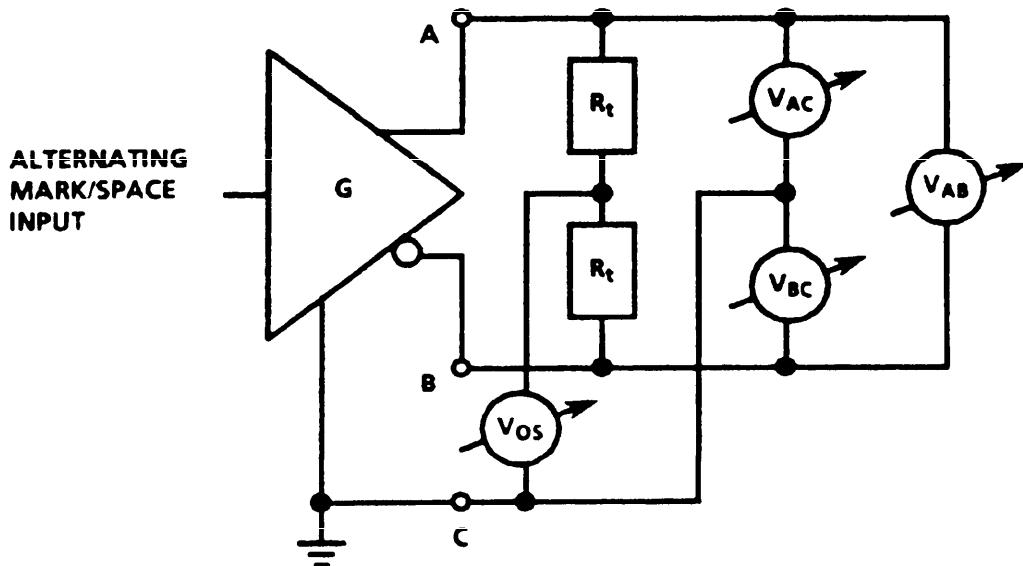

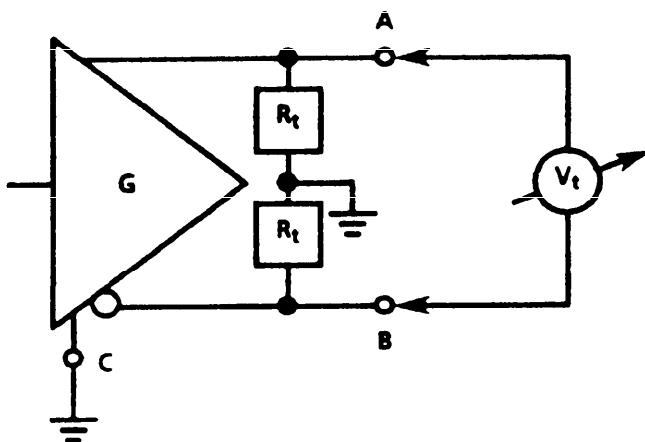

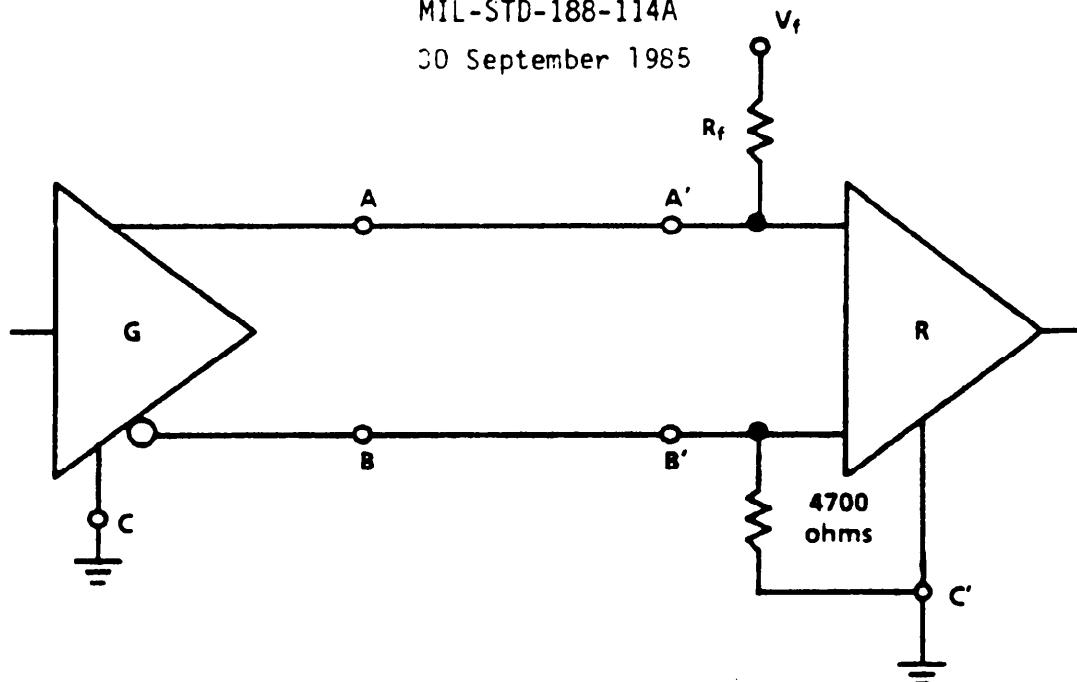

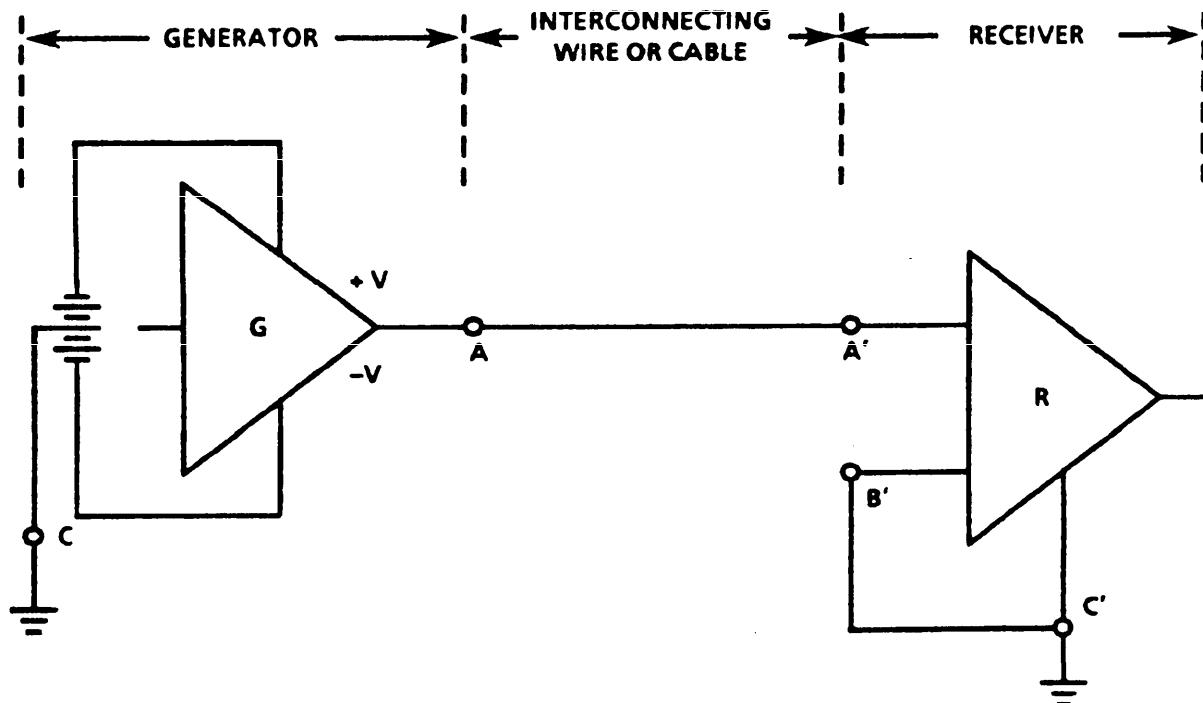

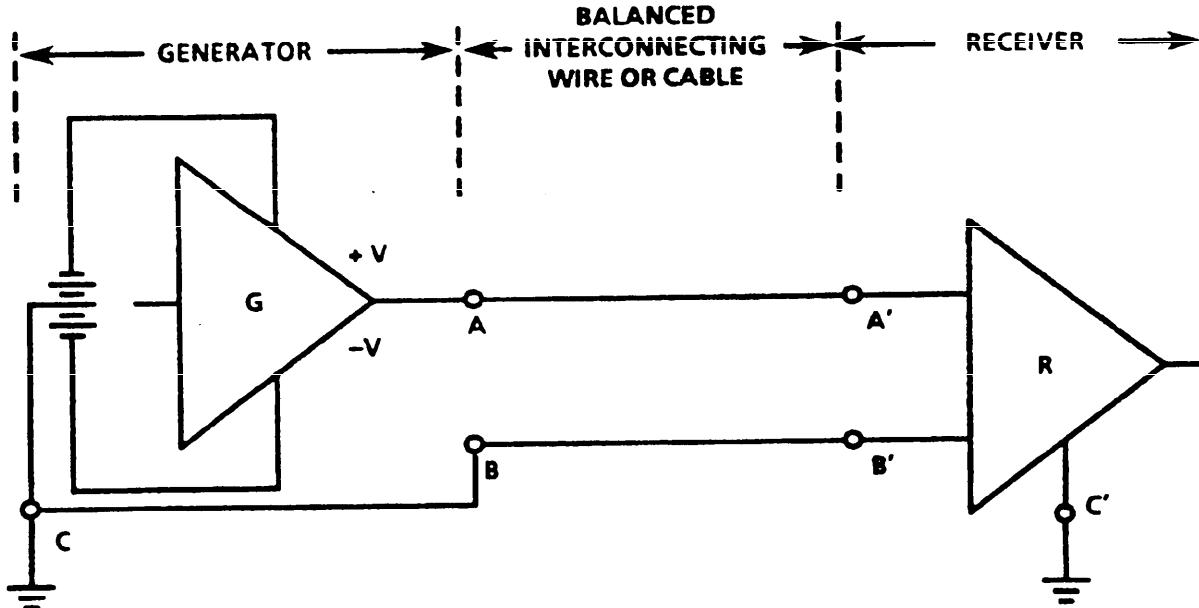

5.2 Balanced voltage digital interface circuit. The balanced voltage digital interface circuit is shown in Figure 10. The circuit consists of three parts: the generator (G) which may be a type I or a type II generator (see 4.4.1), the balanced interconnecting wire or cable, and the load. The load consists of one or more receivers (R) (see 5.2.3.4) and an optional wire or cable termination resistance ( $R_t$ ). The electrical characteristics of the generator and the receiver are specified in terms of direct electrical measurements. Guidance is provided in 30.3 of Appendix C regarding the electrical and physical characteristics of the interconnecting wire or cable.

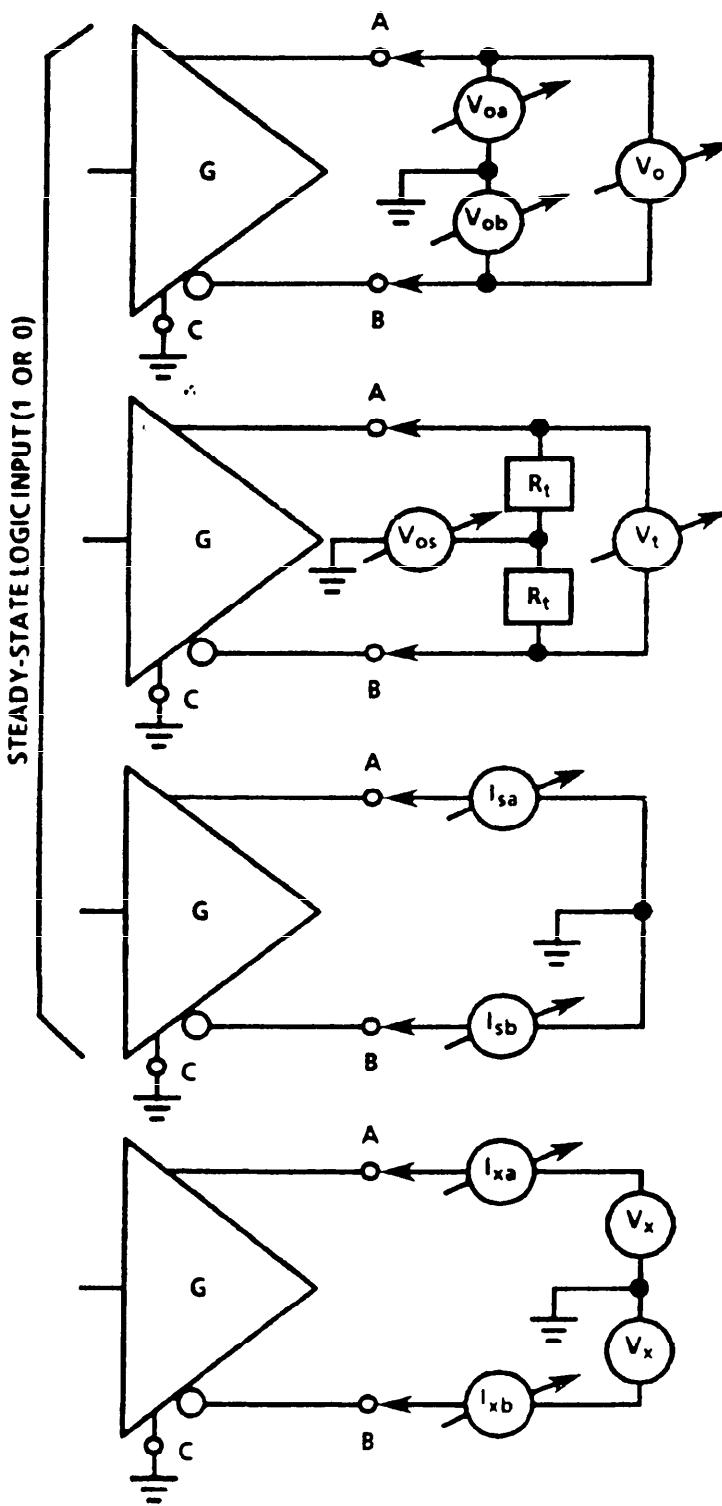

5.2.1 Generator characteristics. The electrical characteristics of the balanced generator are specified in accordance with measurements illustrated in Figures 11, 12 and 13 and described in 5.2.1.1 through 5.2.1.8. The characteristics apply to both type I and type II generators (see 4.4.1) unless otherwise stated in the applicable subparagraph. The measurements are under static conditions, whereas measurements under dynamic conditions are not standardized. A generator meeting these requirements results in a low impedance (100 ohms or less) balanced voltage source that will produce a differential voltage applied to the interconnecting wire or cable in the range of 2 volts to 6 volts.

5.2.1.1 Signal sense. The signal sense of the generator output voltages appearing across the interconnecting wire or cable (see Figure 10) shall be as shown in Table II. (See Note of 5.1.1.1.)

TABLE II. Signal sense for balanced generators

| VOLTAGE POLARITY<br>(See Figures 10 and 14) | DATA       | TIMING          | CONTROL and ALARM |

|---------------------------------------------|------------|-----------------|-------------------|

| Point A negative with respect to point B    | 1 or MARK  | OFF (QUIESCENT) | OFF               |

| Point A negative with respect to point B    | 0 or SPACE | ON (ACTIVE)     | ON                |

5.2.1.2 Signaling rate range. Not standardized. (See 4.3.)

5.2.1.3 Open-circuit measurement. (See Figure 11.) For either binary state, the magnitude of the differential open-circuit voltage ( $V_o$ ) measured between the generator output terminals A and B shall not be less than 4 volts nor more than 6 volts. For type I generators, the magnitudes of the open-circuit voltages  $V_{oa}$  and  $V_{ob}$  measured between the generator output terminals A or B and the generator circuit ground (terminal C) shall not be less than 2 volts nor more than 3 volts. For type II generators, the magnitudes of the

MIL-STD-188-114A

30 September 1985

FIGURE 10. Balanced voltage digital interface circuit.

MIL-STD-188-114A

30 September 1985

**OPEN CIRCUIT MEASUREMENT**

FOR EITHER BINARY STATE:

$$4 \text{ V} \leq |V_0| \leq 6 \text{ V}$$

$$\text{TYPE I: } 2 \text{ V} \leq |V_{0s}| \leq 3 \text{ V}$$

$$2 \text{ V} \leq |V_{0b}| \leq 3 \text{ V}$$

$$\text{TYPE II: } |V_{0s}| \leq 6 \text{ V}$$

$$|V_{0b}| \leq 6 \text{ V}$$

**TEST TERMINATION MEASUREMENT**

FOR EITHER BINARY STATE:

$$|V_t| \geq 0.5 |V_0|$$

$$||V_t - |V_0|| \leq 0.4 \text{ V}$$

$$|V_{0s} - V_{0b}| \leq 0.4 \text{ V}$$

$$\text{TYPE I: } |V_{0s}| \leq 0.4 \text{ V}$$

$$\text{TYPE II: } |V_{0s}| \leq 3 \text{ V}$$

**SHORT CIRCUIT MEASUREMENT**

FOR EITHER BINARY STATE:

$$|I_{sa}| \leq 150 \text{ mA}$$

$$|I_{sb}| \leq 150 \text{ mA}$$

**POWER-OFF MEASUREMENT**

$$|I_{xa}| \leq 100 \mu\text{A}$$

$$|I_{xb}| \leq 100 \mu\text{A}$$

$V_x$  IS APPLIED VOLTAGE

$$\text{TYPE I: } V_x \text{ FROM } -6 \text{ V TO } +6 \text{ V}$$

$$\text{TYPE II: } V_x \text{ FROM } -0.25 \text{ V TO } +6 \text{ V}$$

FIGURE 11. Balanced generator parameter measurements.

MIL-STD-188-114A

30 September 1985

open-circuit voltages  $V_{oa}$  and  $V_{ob}$  measured between the generator output terminals A or B and the generator circuit ground (terminal C) shall not be more than 6 volts.

5.2.1.4 Test termination measurement. (See Figure 11.) With a test load of two resistors, 50 ohms  $\pm 1$  percent each, connected in series between the generator output terminals A and B, the magnitude of the differential voltage  $V_t$  measured between the output terminals A and B shall not be less than one-half of the absolute value of  $V_o$  (see 5.2.1.3). For the opposite binary state the polarity of  $V_t$  shall be reversed ( $\bar{V}_t$ ). The magnitude of the difference of the absolute values of  $V_t$  and  $\bar{V}_t$  shall not be more than 0.4 volts. The magnitude of the difference of  $V_{os}$  for one binary state and  $\bar{V}_{os}$  for the opposite binary state shall not be more than 0.4 volts. For type I generators (see 4.4.1), the magnitude of the generator offset voltage  $V_{os}$  measured between the center point of the test load and generator circuit ground (terminal C) shall not be more than 0.4 volts for either binary state. For type II generators (see 4.4.1), the magnitude of the generator offset voltage  $V_{os}$  shall not be more than 3 volts for either binary state.

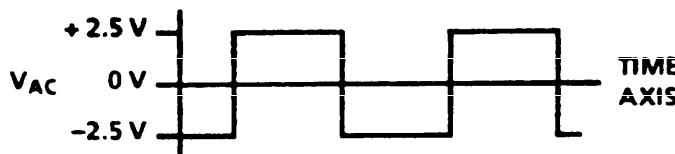

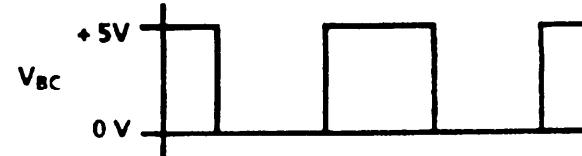

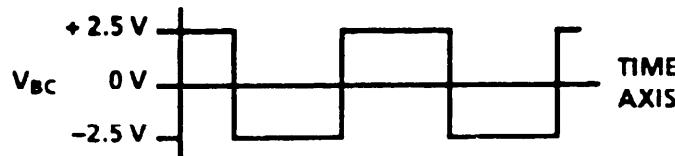

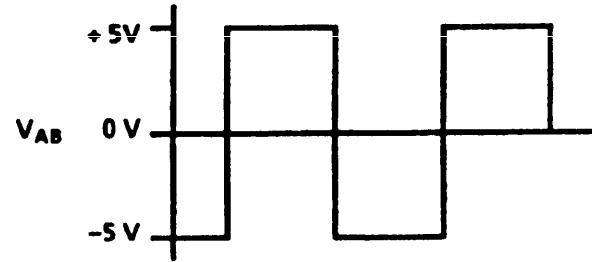

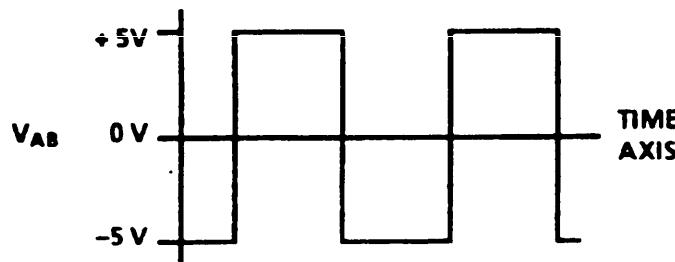

NOTE: Nominal voltage waveforms for alternating binary states are shown in Figure 12 for type I and type II generators (see 4.4.1). These waveforms are intended to represent a typical balanced generator output signal, such as displayed on an oscilloscope.

5.2.1.5 Short-circuit measurement. (See Figure 12.) With the generator output terminals A and B short-circuited to generator circuit ground (terminal C), the magnitudes of the currents flowing through each generator output terminal shall not exceed 150 mA for either binary state.

5.2.1.6 Power-off measurement. (See Figure 12.) Under power-off conditions, the magnitude of the generator output leakage current  $I_{xa}$  and  $I_{xb}$  shall not exceed 100 microamperes with a voltage  $V_x$  applied between each generator output terminal A or B and generator circuit ground (terminal C). For type I generators (see 4.4.1) the terminal AC/BC voltages  $V_x$  shall range between +6 volts and -6 volts, and for type II generators the terminal AC/BC voltages  $V_x$  shall range between +6 volts and -0.25 volts.

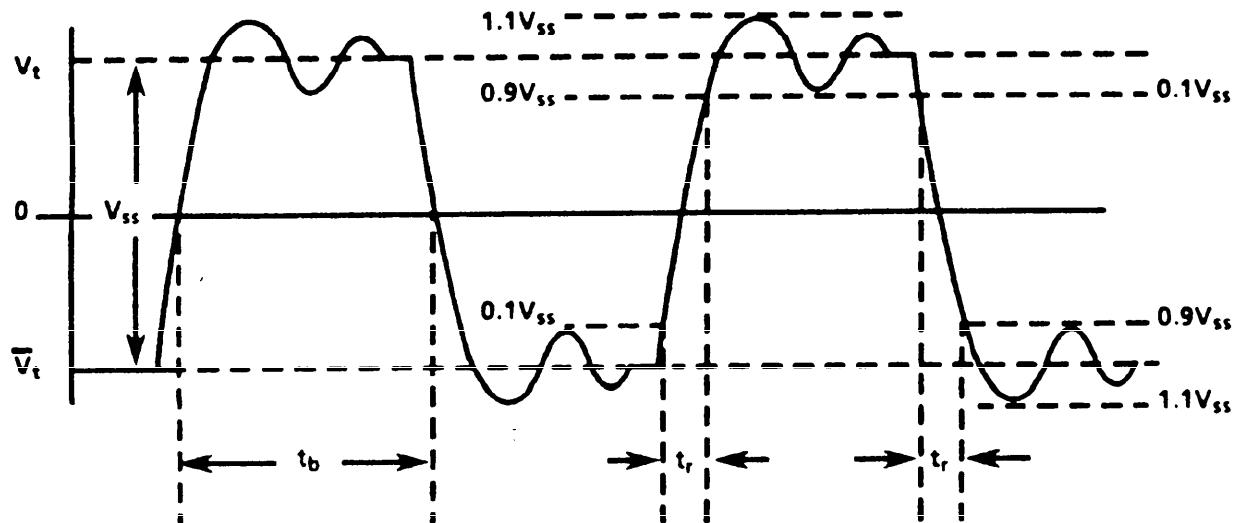

5.2.1.7 Output signal waveform. (See Figure 13.) During transitions of the generator output between alternating binary states (one-zero-one-zero, etc.), the differential signal measured across a 100 ohms  $\pm 10$  percent test load connected between the generator output terminals A and B shall be such that the voltage monotonically changes between 0.1 and 0.9 of  $V_{ss}$  within 0.1 of the unit interval  $t_b$  or 20 nanoseconds (ns), whichever is greater. Thereafter, the signal voltage shall not vary more than 10 percent of  $V_{ss}$  from the steady state value, until the next binary transition occurs, and at no time

MIL-STD-188-114A

30 September 1985

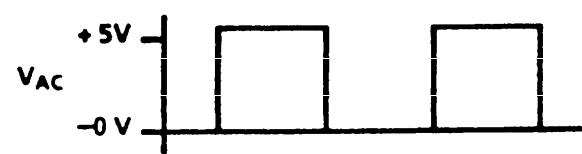

**TYPE I GENERATOR**

ASSUMPTION:  $|V_{AB}| = 5$  V

$|V_{OS}| = 0$  V

**TYPE II GENERATOR**

ASSUMPTION:  $|V_{AB}| = 5$  V

$|V_{OS}| = 2.5$  V

FIGURE 12. Nominal waveforms of type I and type II generators.

MIL-STD-188-114A

30 September 1985

LEGEND:  $R_t$  = 100 ohms,  $\pm 10$  PERCENT

$|V_{ss}|$  =  $|V_t - \bar{V}_t|$

$V_{ss}$  = DIFFERENCE IN STEADY STATE VOLTAGES

$t_b$  = UNIT INTERVAL

$t_r$  = RISETIME

$t_r \leq 0.1 t_b$  OR 20 ns, WHICHEVER IS GREATER

FIGURE 13. Balanced generator output signal waveform.

MIL-STD-188-114A

30 September 1985

shall the instantaneous magnitude of  $V_t$  or  $\bar{V}_t$  exceed 6 volts, nor be less than 2 volts.  $V_{ss}$  is defined as the voltage difference between the two terminated steady state values ( $V_t$  and  $\bar{V}_t$ ) of the generator output.

NOTE: The lower limit of the risetime  $t_r$  is not standardized. The upper limit of the risetime  $t_r$  is either 0.1 of the unit interval  $t_b$  or 20 ns, whichever is greater.

5.2.1.8 High impedance output state. The generator output should be permitted to assume a high impedance state, if required for multiple generator bus operation. If a high impedance state is implemented, the output voltage shall be nominally zero for the high impedance state when measured with a test termination as stated in 5.2.1.4.

5.2.2 Wire or cable characteristics. Not standardized.

Note: Guidelines on wire or cable characteristics are given in 30.3 of Appendix C.

5.2.3 Load characteristics. The load consists of one or more receivers ( $R$ ) and an optional wire or cable termination resistance ( $R_t$ ) as shown in Figure 10. Guidelines on the need for a wire or cable termination resistance are given in 30.4 of Appendix C. The electrical characteristics of a single receiver without optional wire or cable termination and fail safe provision are specified in terms of the measurements illustrated in Figures 7 through 9 and described in 5.1.3.1 through 5.1.3.3. A device meeting these requirements results in a differential receiver having a high input impedance (4000 ohms or more), a small input threshold transition region between -0.2 volts and +0.2 volts, and allowance for an internal bias voltage not to exceed 3 volts in magnitude. Multiple receivers and a provision for fail safe operation for specific applications are allowed in the load within the limitations specified in 5.2.3.6. The receiver used in the load for the balanced voltage digital interface circuit is electrically identical to the receiver for the unbalanced voltage digital interface circuit stated in 5.1 and for the terminated voltage digital interface circuit stated in 5.3.

5.2.3.1 Receiver input current-voltage measurement. Same as 5.1.3.1.

5.2.3.2 Receiver input sensitivity measurement. Same as 5.1.3.2.

5.2.3.3 Receiver input balance measurement. Same as 5.1.3.3.

5.2.3.4 Multiple receivers. Not standardized.

NOTE: The use of up to ten receivers in the load may be optionally employed. Extreme caution must be exercised to avoid performance degradation due to signal reflections from stub lines emanating from the load interface point to the receivers. See 5.2.3.6 for limits on total load resistance and sensitivity.

MIL-STD-188-114A

30 September 1985

5.2.3.5 Fail-safe operation. Where a fail-safe is required, a provision shall be incorporated in the load to provide a steady binary condition (either MARK or SPACE as required by the application) to protect against certain fault conditions.

NOTE: The method of providing fail-safe is not standardized. An example of fail-safe operation is given in 30.5.2 of Appendix C.

5.2.3.6 Total load characteristic limits. The total load, including multiple receivers, fail-safe provisions, and wire or cable termination (if implemented), shall have a resistance greater than 120 ohms between its input points (terminals A' and B' of Figure 10) and shall require a differential input voltage of not more than 200 mV for all receivers to assume the intended binary state.

5.2.3.7 Wire or cable termination resistance. Not standardized.

NOTE: The use of a wire or cable termination resistance ( $R_t$ ) is optional, depending upon the specific environment in which the interface circuit is employed. See 5.2.3.6 for limits on total load resistance and 30.4 of Appendix C for guidelines on the need for a wire or cable termination resistance.

5.2.4 Operational constraints. A balanced voltage digital interface circuit conforming to 5.2 will perform satisfactorily at signaling rates up to 10 Mb/s providing that the following operational constraints are simultaneously satisfied:

- a. The interconnecting wire or cable length is within that recommended for the applicable signaling rate indicated in 30.3.6 of Appendix C, and the wire or cable is appropriately terminated.

- b. The common mode voltage at the receiver is less than 7 volts (peak). The common mode voltage is defined to be any uncompensated combination of generator-receiver ground potential difference, the generator offset voltage  $V_{os}$ , and longitudinally coupled peak random noise voltage measured between the receiver circuit ground and the wire or cable with the generator ends of the wire or cable short-circuited to ground.

NOTE 1: The use of type II generators with up to 3 volts of offset voltage will reduce the common mode noise protection margin by an amount proportional to the value of the offset voltage.

NOTE 2: Care should be taken when power for distant receivers is supplied in the same or in adjacent conductors as used for data, clock or control signals, in order to avoid performance degradation that may be caused by power supply surges and spurious voltage transients.

MIL-STD-188-114A

30 September 1985

5.2.5 Circuit protection. Same as 5.1.5.

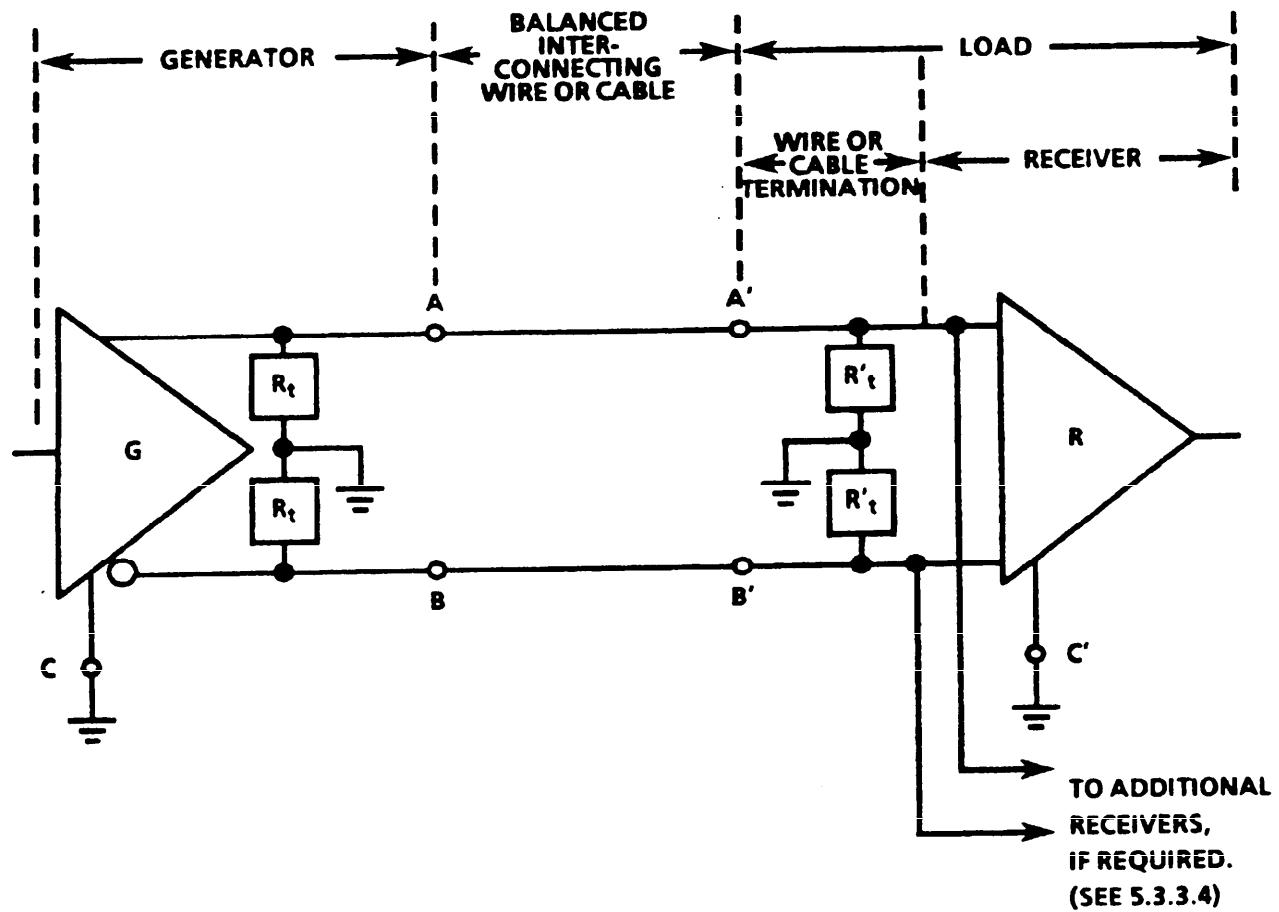

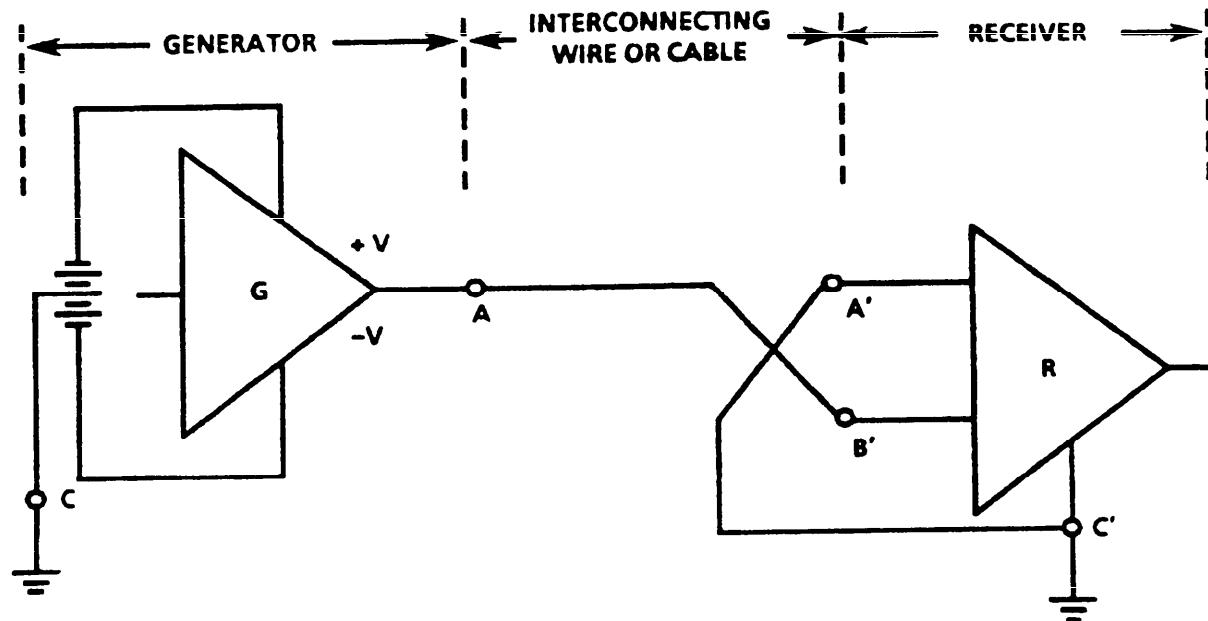

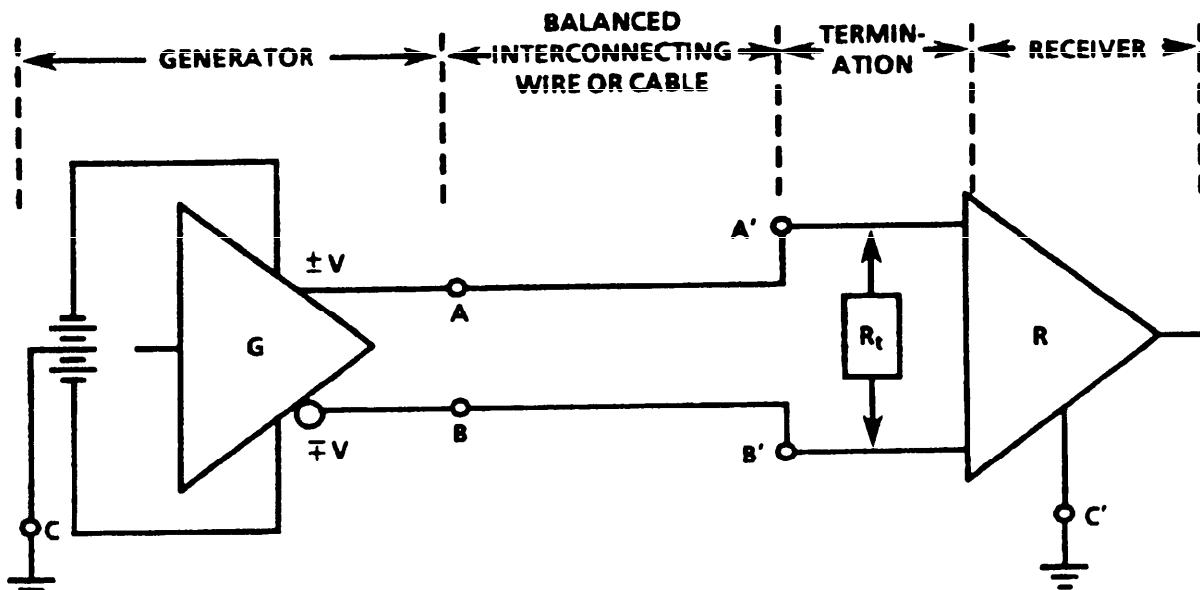

5.3 Terminated voltage digital interface circuit. The terminated voltage digital interface circuit is a balanced voltage circuit and is shown in Figure 14. The circuit consists of three parts: the terminated voltage generator (G) which is a type III generator (see 4.4.1), the balanced interconnecting wire or cable, and the load. The terminated voltage generator requires a termination resistance ( $R_t$ ), with a grounded center tap. The termination resistance ( $R_t$ ), although external to the generator, is considered to be part of the generator circuit and is necessary to match the relatively high generator source impedance to the characteristic impedance of the transmission line. A similar type termination is also required at the end of the transmission line where the receiver is connected. The terminated voltage generator has characteristics similar to, and may be treated like, a constant-current generator, although the actual implementation may not be a true constant-current generator. It should be noted that the use of a termination at the constant-current generator output actually causes a voltage waveform to be generated which in turn drives the transmission line. The voltage polarity reverses when the current direction changes. The advantage of this circuit configuration is that the rise and fall time of the voltage waveform is primarily determined by the constant-current generator and is relatively unaffected by the transmission line characteristics, which is important for signaling rates above 10 Mb/s. The load consists of one or more receivers (R), (see 5.3.3.4) and a wire or cable termination resistance ( $R_t'$ ). The termination resistance ( $R_t'$ ) is selected to match the characteristic impedance of the transmission line to the relatively high input impedance of the receiver.

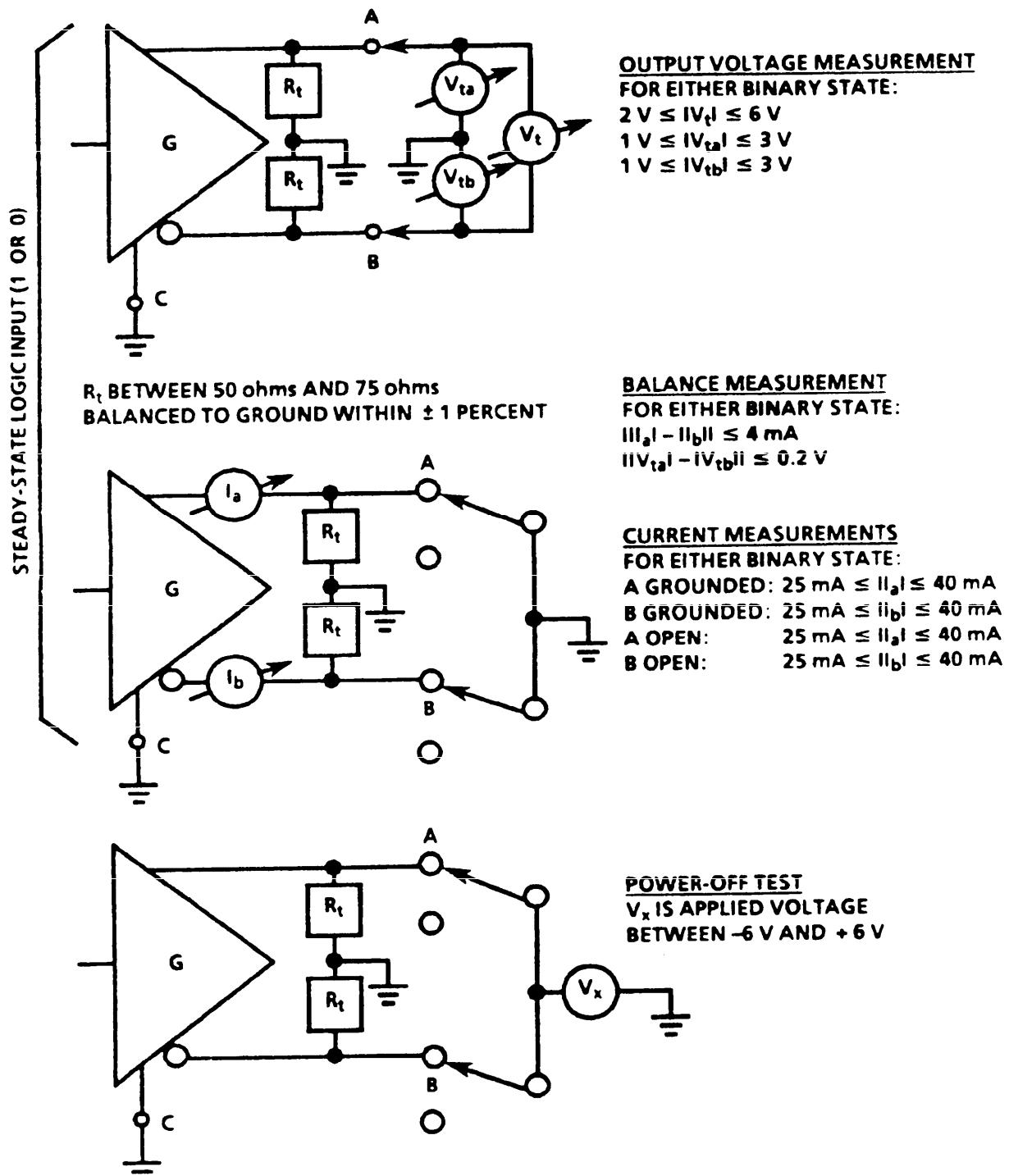

5.3.1 Generator characteristics. The electrical characteristics of the type III generator (see 4.4.1) are specified in accordance with the measurements illustrated in Figures 15 and 16 and described in 5.3.1.1 through 5.3.1.7. The measurements are under static conditions, whereas measurements under dynamic conditions are not standardized. A generator meeting these requirements results in a low impedance (150 ohms or less) balanced voltage source that will produce a differential voltage applied to the interconnecting wire or cable in the range of 2 volts to 6 volts.

5.3.1.1 Signal sense. The signal sense of the generator output voltages appearing across the interconnecting wire or cable (see Figure 14) shall be as shown in Table II. (See Note of 5.1.1.1.)

5.3.1.2 Signaling rate range. Not standardized. (See 4.3.)

5.3.1.3 Output voltage measurement. (See Figure 15.) With a termination of two resistors ( $R_t$ ), each between 50 ohms and 75 ohms, connected in series between the generator output terminals A and B and balanced to ground within  $\pm 1$  percent, the magnitude of the differential voltage ( $V_t$ ) measured between the generator output terminals A and B shall not be less than 2 volts nor

MIL-STD-188-114A

30 September 1985

FIGURE 14. Terminated voltage digital interface circuit.

MIL-STD-188-114A

30 September 1985

FIGURE 15. Terminated voltage generator parameter measurements.

MIL-STD-188-114A

30 September 1985

more than 6 volts for either binary state. The magnitudes of  $V_{ta}$  and  $V_{tb}$  measured between the generator output terminals A or B and the generator circuit ground (terminal C) shall not be less than 1 volt nor more than 3 volts.

5.3.1.4 Balance measurement. (See Figure 15.) With a termination of two resistors ( $R_t$ ), each between 50 ohms and 75 ohms, connected in series between the generator output terminals A and B and balanced to ground within  $\pm 1$  percent, the magnitude of the difference of the absolute values of  $I_a$  and  $I_b$  shall be less than or equal to 4 mA. The current balance shall be verified by measuring the voltage drops  $V_{ta}$  and  $V_{tb}$ . The magnitude of the difference of the absolute values of  $V_{ta}$  and  $V_{tb}$  shall be less than or equal to 0.2 volts, for either binary state.

5.3.1.5 Current measurements. (See Figure 15.) With the generator output terminal A or B, or both, short-circuited (grounded) to generator circuit ground (terminal C) or open (ungrounded), the magnitudes of the currents  $I_a$  and  $I_b$  flowing through each generator output terminal shall not be less than 25 mA nor more than 40 mA for either binary state. The magnitude of the difference of the absolute values of the grounded and ungrounded (open) generator currents  $I_a$  and  $I_b$  shall be less than or equal to 4 mA for either binary state.

5.3.1.6 Power-off test. (See Figure 15.) Under power-off conditions, the generator shall not be damaged by an external voltage  $V_x$  ranging between +6 volts and -6 volts applied between either or both output terminals A and B and generator circuit ground (terminal C).