## **DOT/FAA/TC-14/49**

Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405

# Selection of Cyclic Redundancy Code and Checksum Algorithms to Ensure Critical Data Integrity

March 2015

Final Report

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

U.S. Department of Transportation Federal Aviation Administration

## **NOTICE**

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

**Technical Report Documentation Page**

| Report No.                                                         | Government Accession No. | Recipient's Catalog No.               |

|--------------------------------------------------------------------|--------------------------|---------------------------------------|

| DOT/FAA/TC-14/49                                                   |                          |                                       |

| 4. Title and Subitle                                               |                          | 5. Report Date                        |

| SELECTION OF CYCLIC REDUNDANG                                      | CY CODE AND CHECKSUM     | March 2015                            |

| ALGORITHMS TO ENSURE CRITICAL                                      | L DATA INTEGRITY         | Performing Organization Code          |

|                                                                    |                          | 220410                                |

| 7. Author(s)                                                       |                          | Performing Organization Report No.    |

| Philip Koopman <sup>1</sup> , Kevin Driscoll <sup>2</sup> , Brenda | an Hall <sup>2</sup>     |                                       |

| Performing Organization Name and Address                           |                          | 10. Work Unit No. (TRAIS)             |

| <sup>1</sup> Carnegie Mellon University                            |                          |                                       |

| 5000 Forbes Ave., Pittsburgh, PA 15213 U                           | USA                      |                                       |

|                                                                    |                          |                                       |

| <sup>2</sup> Honeywell Laboratories                                |                          | 11. Contract or Grant No.             |

| 1985 Douglas Drive North, Golden Valley                            | y, MN 55422 USA          | DTFACT-11-C-00005                     |

|                                                                    |                          |                                       |

| 12. Sponsoring Agency Name and Address                             |                          | 13. Type of Report and Period Covered |

| U.S. Department of Transportation                                  |                          | Final Report, August 2011-April 2013  |

| Federal Aviation Administration                                    |                          |                                       |

| 950 L'Enfant Plaza SW, 5 <sup>th</sup> Floor                       |                          |                                       |

| Washington, DC 20024                                               |                          |                                       |

|                                                                    |                          | 14. Sponsoring Agency Code\           |

|                                                                    |                          | AIR-134                               |

15. Supplementary Notes

The Federal Aviation Administration Aviation Research Division COR was Charles Kilgore.

16. Abstract

This report explores the characteristics of checksums and cyclic redundancy codes (CRCs) in an aviation context. It includes a literature review, a discussion of error detection performance metrics, a comparison of various checksum and CRC approaches, and a proposed methodology for mapping CRC and checksum design parameters to aviation integrity requirements. Specific examples studied are Institute of Electrical and Electronics Engineers (IEEE) 802.3 CRC-32; Aeronautical Radio, Incorporated (ARINC)-629 error detection; ARINC-825 Controller Area Network (CAN) error detection; Fletcher checksum; and the Aeronautical Telecommunication Network (ATN)-32 checksum. Also considered are multiple error codes used together, specific effects relevant to communication networks, memory storage, and transferring data from nonvolatile to volatile memory.

Key findings include: (1) significant differences exist in effectiveness between error-code approaches, with CRCs being generally superior to checksums in a wide variety of contexts; (2) common practices and published standards may provide suboptimal (or sometimes even incorrect) information, requiring diligence in selecting practices to adopt in new standards and new systems; (3) error detection effectiveness depends on many factors, with the Hamming distance of the error code being of primary importance in many practical situations; (4) no one-size-fits-all error-coding approach exists, although this report does propose a procedure that can be followed to make a methodical decision as to which coding approach to adopt; and (5) a number of secondary considerations must be taken into account that can substantially influence the achieved error-detection effectiveness of a particular error-coding approach.

| 17. Key Words                                                                                                 |                                | 18. Distribution Statement              |                                                                 |                                                                                          |

|---------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| CRC, Cyclic redundancy code, Checksum, Error coding, Error detection, Network data errors, Memory data errors |                                | National Technical<br>Virginia 22161. T | Information Service This document is all Imministration William | S. public through the e (NTIS), Springfield, so available from the m J. Hughes Technical |

| 19. Security Classif. (of this report)                                                                        | 20. Security Classif. (of this | page)                                   | 21. No. of Pages                                                | 22. Price                                                                                |

| Unclassified Unclassified                                                                                     |                                |                                         | 111                                                             |                                                                                          |

#### **ACKNOWLEDGEMENTS**

The authors would like to thank the following people for their contributions to this project and the underlying work upon which it was based:

- Justin Ray, Carnegie Mellon University

- Theresa Maxino, Carnegie Mellon University

- Tridib Chakravarty, Carnegie Mellon University

- Pavan Allalaghatta, Honeywell

The authors would like to acknowledge the following Federal Aviation Administration Review Team individuals for providing support to the project:

- Liz Brandli

- Michael P. DeWalt

- Gary Horan

- Charles Kilgore

- Barbara Lingberg

- Srini Mandalapu

- Steve Paasch

- John Strasburger

- Will Struck

The authors would also like to thank the anonymous contributors who provided valuable information during our industry data collection.

## TABLE OF CONTENTS

|     |                                                              |                                                                                                                                                                                                                                                                                                                                   | Page                                                           |

|-----|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| EXE | CUTIVE S                                                     | SUMMARY                                                                                                                                                                                                                                                                                                                           | xi                                                             |

| 1.  | INTRO                                                        | DUCTION                                                                                                                                                                                                                                                                                                                           | 1                                                              |

|     | 1.2                                                          | Purpose<br>Background<br>Related Activities, Documents, Symbology, and Terminology                                                                                                                                                                                                                                                | 1<br>1<br>2                                                    |

| 2.  | METH                                                         | ODOLOGY AND VALIDITY                                                                                                                                                                                                                                                                                                              | 2                                                              |

|     |                                                              | Fault Model and Undetected Errors Error Detection Performance Criteria                                                                                                                                                                                                                                                            | 2 3                                                            |

|     |                                                              | <ul> <li>2.2.1 Coding Design Parameters</li> <li>2.2.2 Potential Evaluation Criteria</li> <li>2.2.3 Application Attributes</li> <li>2.2.4 Other Factors</li> </ul>                                                                                                                                                                | 3<br>3<br>4<br>5                                               |

|     | 2.4<br>2.5                                                   | The Adopted Fault Model Checksum Evaluation The CRC Evaluation Other Evaluations                                                                                                                                                                                                                                                  | 5<br>7<br>10<br>11                                             |

| 3.  | CHECH                                                        | KSUM AND CRC ERROR DETECTION                                                                                                                                                                                                                                                                                                      | 11                                                             |

|     | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Random Hash HD = 1 Error Detection Parity Longitudinal Redundancy Check Two's Complement Checksum One's Complement Checksum Fletcher Checksum Adler Checksum The ATN-32 The CRC Other Error-Detection Considerations  3.10.1 Effect of Initial Seed Values 3.10.2 Burst Error Detection 3.10.3 Detection of Changes in Data Order | 11<br>12<br>13<br>15<br>16<br>17<br>21<br>22<br>24<br>27<br>27 |

| 1   |                                                              | TON-SPECIFIC RESULTS                                                                                                                                                                                                                                                                                                              | 28                                                             |

|    | 4.1   | The ARINC-629                                         | 29 |

|----|-------|-------------------------------------------------------|----|

|    | 4.2   | The ARINC-825                                         | 29 |

| 5. | FRAM  | MING, ENCODING, AND MULTIPLE CRCs                     | 30 |

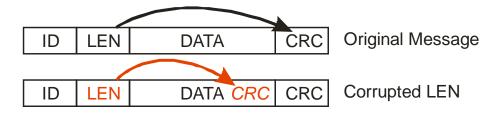

|    | 5.1   | Corrupted Length Field                                | 30 |

|    | 5.2   | Bit Stuff Vulnerabilities                             | 30 |

|    | 5.3   | Balance Bit Encoding                                  | 31 |

|    | 5.4   | Data Scramblers                                       | 31 |

|    | 5.5   | Encryption                                            | 32 |

|    | 5.6   | Memory Data Placement Effects                         | 32 |

|    | 5.7   | Multiple Checksums and CRCs                           | 32 |

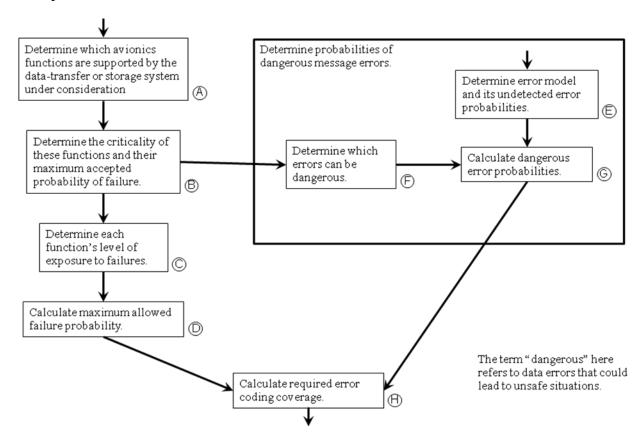

| 6. | MAP   | PING CRITICALITY TO INTEGRITY COVERAGE                | 33 |

|    | 6.1   | Importance of Coverage Determination                  | 33 |

|    | 6.2   | Scope                                                 | 34 |

|    | 6.3   | Data-Transfer System Guidance Background              | 35 |

|    | 6.4   | Mapping Process Overview                              | 35 |

|    | 6.5   | Example Avionics Data-Transfer System                 | 36 |

|    | 6.6   | Criticality Mapping Flow, Steps A and B               | 37 |

|    |       | 6.6.1 Criticality Mapping Flow, Steps A and B Example | 37 |

|    | 6.7 C | riticality Mapping Flow, Step C                       | 37 |

|    |       | 6.7.1 Criticality Mapping Flow, Step C Example        | 37 |

|    | 6.8   | Criticality Mapping Flow, Step D                      | 37 |

|    |       | 6.8.1 Criticality Mapping Flow, Step D Example        | 38 |

|    | 6.9   | Criticality Mapping Flow, Step E.                     | 38 |

|    |       | 6.9.1 Finding a BER                                   | 39 |

|    |       | 6.9.2 The BER Tests                                   | 40 |

|    |       | 6.9.3 The BER Degradation                             | 40 |

|    |       | 6.9.4 Criticality Mapping Flow, Step E Example        | 41 |

|    | 6.10  | Criticality Mapping Flow, Step F                      | 41 |

|    |       | 6.10.1 Criticality Mapping Flow, Step F Example       | 41 |

|    | 6.11  | Criticality Mapping Flow, Step G                      | 41 |

|    |       | 6.11.1 Criticality Mapping Flow, Step G Example       | 41 |

|      | 6.12   | Criticality Mapping Flow, Step H                           | 42 |

|------|--------|------------------------------------------------------------|----|

|      |        | 6.12.1 Criticality Mapping Flow, Step H Example            | 42 |

|      | 6.13   | Error Detection Mechanism Failure                          | 43 |

|      | 6.14   | Other Errors in the Message                                | 43 |

|      | 6.15   | Using HD To Exploit CRCs                                   | 44 |

|      | 6.16   | A Simplified Approach to Coverage                          | 45 |

|      | 6.17   | Data Storage Protection                                    | 45 |

|      | 6.18   | Transfer from NonVolatile to Program RAM                   | 46 |

| 7.   | FUTU   | JRE WORK                                                   | 47 |

| 8.   | RESU   | JLTS                                                       | 48 |

| 9.   | REFE   | ERENCES                                                    | 51 |

| 10.  | GLOS   | SSARY                                                      | 52 |

| APPE | ENDICE | ES                                                         |    |

|      |        | iterature Review and Discussion                            |    |

|      | B—S    | even Deadly Sins for Checksums and Cyclic Redundancy Codes |    |

|      |        | cyclic Redundancy Code and Checksum Tutorial Slides        |    |

|      |        |                                                            |    |

# LIST OF FIGURES

| Figure |                                                    | Page |

|--------|----------------------------------------------------|------|

| 1      | The Pud for LRC and Addition Checksums             | 14   |

| 2      | The 32-Bit Checksum Performance                    | 20   |

| 3      | Fletcher Checksum Performance                      | 21   |

| 4      | The ATN-32 Checksum Algorithm                      | 22   |

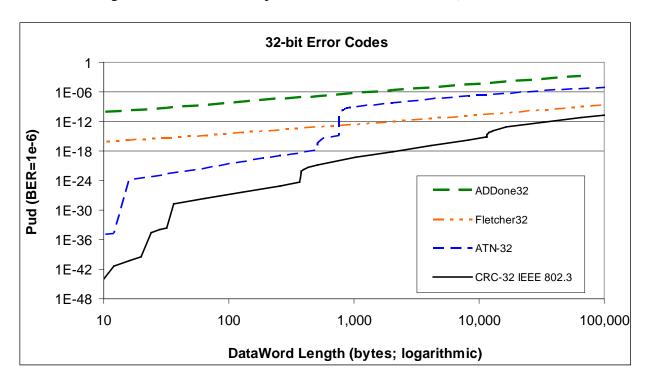

| 5      | The 32-Bit Checksum Compared to ATN-32 Performance | 24   |

| 6      | A 32-Bit Error Code Performance Including CRC-32   | 25   |

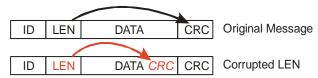

| 7      | Corruption of Message Length Field                 | 30   |

| 8      | Criticality Mapping Flow Diagram                   | 36   |

# LIST OF TABLES

| Table |                                           | Page |

|-------|-------------------------------------------|------|

| 1     | Random Hash Error Detection               | 12   |

| 2     | The LRC Error Detection                   | 14   |

| 3     | Two's Complement Checksum Error Detection | 16   |

| 4     | One's Complement Checksum Error Detection | 17   |

| 5     | Fletcher Checksum Error Detection         | 19   |

| 6     | The ATN-32 Checksum Error Detection       | 23   |

| 7     | Error Detection of Good CRC Polynomials   | 26   |

## LIST OF ACRONYMS AND ABBREVIATIONS

AC Advisory Circular

ARINC Aeronautical Radio, Incorporated

ATN Aeronautical Telecommunication Network

BER Bit error ratio

CAN Controller Area Network

CCITT Comité Consultatif International Téléphonique et Télégraphique

COTS Commercial, Off-the-Shelf CRC Cyclic redundancy code

FAA Federal Aviation Administration

FCS Frame check sequence HD Hamming distance

HDLC High Level Data Link Control

HW Hamming weight

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

IP Internet protocol

Kbytes Kilobytes (1024 bytes—since random-access memory capacity, such as CPU cache

measurements are always stated in multiples of 1024 (210) bytes, due to memory's

binary addressing)

LFSR Linear feedback shift register LRC Longitudinal redundancy check

MIC Message Integrity Check

Modbus Modicon bus NRZ Non-return-to-zero

NUREG Nuclear Regulatory Commission publication

PROFIBUS Process field bus

PROFIsafe Process field bus safety profile Pud Probability of undetected error

RAM Random access memory RFC Request for comment

RTCA RTCA, Inc. (formerly Radio Technical Commission for Aeronautics)

RZ Return-to-zero SAE SAE, Inc.

SCTP Stream Control Transmission Protocol

SIL Safety Integrity Level

TCP Transmission Control Protocol TTP/C Time-Triggered Protocol Version C

UDP User Datagram Protocol

XOR Exclusive OR

#### **EXECUTIVE SUMMARY**

This report explores the characteristics of checksums and cyclic redundancy codes (CRCs) in an aviation context. It includes a literature review; a discussion of error detection performance metrics; a comparison of various checksum and CRC approaches; and a proposed methodology for mapping CRC and checksum design parameters to aviation integrity requirements. Specific examples studied are Institute of Electrical and Electronics Engineers (IEEE) Standard 802.3 CRC-32; Aeronautical Radio, Incorporated (ARINC)-629 error detection; ARINC-825 Controller Area Network error detection; Fletcher checksum; and the Aeronautical Telecommunication Network-32 checksum. Also considered are multiple error codes used together, specific effects relevant to communication networks, memory storage, and transferring data from nonvolatile to volatile memory.

The key findings of the report show that:

- Significant differences in performance between error detection approaches, with CRCs, in many cases, providing dramatically better error-detection capabilities than checksums.

- Common practice and published standards have suboptimal<sup>1</sup> (or sometimes incorrect) information about error detection codes. For example, Fletcher checksums are sometimes said to be as good as a standard CRC, but are often dramatically less effective than a well-chosen CRC. This report provides state-of-the-art information in this area.

- Error detection effectiveness depends on multiple factors, including the size of data to be protected, the types of data errors expected, the smallest number of bit errors that are undetectable by the error code (Hamming distance [HD]), and the undetected error fraction of errors as a function of number of bit errors present in a particular piece of data.

- There is no one-size-fits-all answer as to which error detection code to use. In evaluating error detection capability, a recommended high-level approach is to:

- Understand the acceptable probability of undetected error (Pud)

- Characterize exposure to data faults

- Determine what fraction of dangerous faults will be undetected by a particular error code, given an appropriate fault model

- Determine if the Pud (based on both exposure to faults and fault detection rate) is sufficiently low to meet integrity requirements

<sup>1</sup> The use of the term "suboptimal," when describing a technique, should not be interpreted as indicating that the technique is not suitable for particular purposes.

хi

In determining if undetected error probabilities are low enough, it can be sufficient to pick an error code with an adequately large HD so that all errors expected to occur within a system's operating life are guaranteed to be detected (so long as a random independent fault model accurately reflects the errors that will be seen in operation).

There are a number of other considerations, constraints, and system-level issues that must be considered. These include:

- The need to scrub error detection mechanisms and data values to mitigate the risk of fault accumulation over time

- Vulnerabilities due to message framing (e.g., corrupted length field undermining CRC effectiveness)

- Vulnerabilities due to bit encoding (e.g., stuff bits, multi-bit symbols, or scrambling undermining CRC HD)

- Potential bit error correlations due to memory geometry

- Complex intermediate processing stages potentially invalidating an assumption of unpatterned, random independent bit errors

#### 1. INTRODUCTION.

## 1.1 PURPOSE.

This document is the final report of a task to create a comparative summary of checksum and Cyclic Redundancy Code (CRC) performance in an aviation context. Specific goals are to perform a literature review of evaluation criteria, parameters, and tradeoffs; study CRC and checksum performance with respect to their design parameters and achieved error detection performance; recommend a way to relate CRC and checksum design parameters to functional integrity levels; and make recommendations for future research work.

This report also briefly addresses additional areas vital to correct application of error detection codes in practice. These areas include the effects of data encoding formats on error detection code effectiveness and the error detection effectiveness of using multiple error codes. The scope of the report is limited to checksums and CRCs.

## 1.2 BACKGROUND.

While checksums and CRCs have been in use for many years (the seminal CRC reference dates back to 1957 [1]), published research into their effectiveness is sparse. Additionally, many different application domains, including aviation, use a wide variety of data-integrity approaches that do not necessarily correspond to published best practices. In part, this seems to be because of computational costs that have historically limited the ability to evaluate CRC performance. Another factor is a communication gap between mathematical discussions of the techniques and what practitioners need to successfully apply those techniques to aviation and other domains. Often, it is simply because of practitioners copying problematic error detection techniques already in use under the incorrect assumption that widely used approaches must be good approaches. The research covered by this report is intended to address these issues.

The general approach of this research was to complete the following steps:

- 1. Perform a literature review to identify relevant error detection coding techniques and candidate evaluation criteria for checksums and CRCs.

- 2. Consider representative aviation applications available to the authors, including data characteristics, usage scenarios, and fault exposure.

- 3. Evaluate error detection code effectiveness via simulation and analysis.

- 4. Suggest a strategy for mapping error-detection effectiveness to functional integrity levels.

- 5. Identify topics for future work.

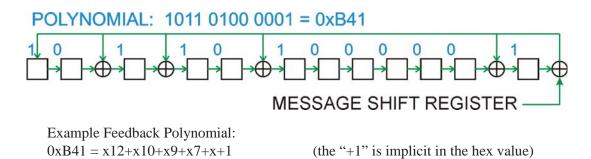

A tutorial on checksums and CRCs was created to provide technical background and is included in presentation slide format as appendix C of this report.

## 1.3 RELATED ACTIVITIES, DOCUMENTS, SYMBOLOGY, AND TERMINOLOGY.

The Statement of Work for this project specifically identifies Koopman and Chakravarty [2] as the basis for the literature review. A literature review with a description of more detailed publications in this area can be found in section 7.

The Glossary section of this report provides working definitions for terminology.

To minimize complex typography, scientific notation using calculator-style "e" notation has been used. For example, "2.36e-6" is 2.36 times 10 raised to the -6 power, equivalent to the number 0.00000236. For CRC polynomials, the exponentiation symbol "^" has been used in keeping with the most common convention for that type of mathematics. The CRC polynomials are not evaluated to produce numeric answers in this report, whereas the scientific notation numbers and the other uses of exponentiation are numerically evaluated.

In this report, the terms "fault" and "error" are used interchangeably with regard to data corruption, which is common in this area of study, but does not necessarily encompass the distinctions made between those terms in system-level dependability studies.

## 2. METHODOLOGY AND VALIDITY.

## 2.1 FAULT MODEL AND UNDETECTED ERRORS.

The principal purpose of this work is to understand how often undetected errors can occur and how to relate that information to integrity levels. The fault model is a binary symmetric channel with bit inversion faults (sometimes called a "bit flip" fault model). In other words, a data value is represented in bits and each bit error results in a single bit value being inverted from 0 to 1 or from 1 to 0.

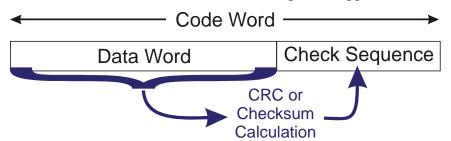

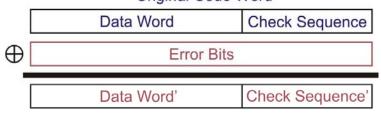

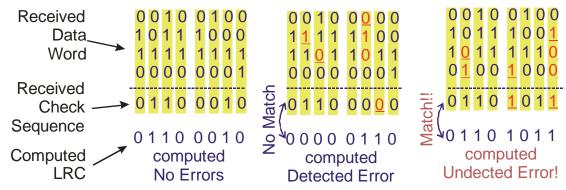

An undetected error is considered to have occurred when a corrupted codeword is valid. A codeword is the concatenation of a particular dataword and the corresponding computational result of the error coding approach, which is the check sequence or frame check sequence (FCS). A codeword can be corrupted by inverting one or more bits in it. These bit corruptions can affect the dataword, the FCS, or both. The corrupted codeword can then be checked to see if it is a valid codeword. In other words, after corruption, there is an error check to see whether the error-detection computation, when performed upon the corrupted dataword, generates a value that matches the corrupted FCS. If the corrupted FCS value from the codeword correctly matches the error-coding calculation performed on the corrupted dataword, the error is undetectable using that error-coding scheme. For an error to be undetectable in codes considered in this work, the dataword must be corrupted, but the FCS may or may not be corrupted to create a codeword with an undetectable error.

Relevant parameters in determining error-detection capabilities of a particular coding scheme include the size of the dataword, the size of the FCS, the number of erroneous bits, and, in some cases, the dataword value before corruption.

Another fault model discussed is that of a burst error, in which two or more bits within a given portion of the codeword are corrupted. For example, a 32-bit burst error has two or more bits in error within a span of 32 bits of the corrupted dataword. Error codes have a burst error detection capability, but, in that usage, detectable burst errors are smaller than or equal to the maximum detectable burst error size. For example, if an error code has 32-bit burst error detection capability, it can also detect all 31-bit, 30-bit, and smaller burst errors.

There are other fault models possible, such as bit slip in communication networks, in which a bit is effectively replicated or deleted from the middle of a bit stream. Those fault models are beyond the scope of this report, although an example of a fault model related to the bit-slip fault is discussed in section 5.2.

## 2.2 ERROR DETECTION PERFORMANCE CRITERIA.

A study of various error-detection performance criteria mentioned in the literature was performed (see section 7 for a more thorough discussion of sources), and numerous possible criteria were identified. The potential criteria include:

## 2.2.1 Coding Design Parameters.

- The FCS size 8, 16, 24, 32 bits or other

- Maximum dataword size to be protected and dataword size probability distribution

- Error type: (bisymmetric burst, erasure burst, bit error ratio (BER) bisymmetric, BER random erasure, random data, leading zeros, bit insertion/deletion, bit slip)

- Coding type: (Parity, exclusive OR [XOR], Add, one's complement Add, Fletcher, Adler, Aeronautical Telecommunication Network [ATN] checksum, CRC, cryptographic hash function, multiple CRCs, checksum+CRC)

- Bit encoding: return-to-zero (RZ), non-return-to-zero (NRZ), 8B/10B, bit stuff, start/stop bits

- Interacting design considerations: {bit slip, stuff bits, length field protection, value imbalance}

- Seed values and similar (e.g., to avoid all-zero codewords or to mitigate masquerade attacks)

## 2.2.2 Potential Evaluation Criteria.

- Hamming distance (HD)

- Hamming weights (HWs)

- Probability of undetected error (Pud) for specified BER and dataword length

- Burst error detection (longest burst for which all errors are caught)

- Burst error performance (HD for a given burst length)

- Shortest dataword size for undetected k-bit error (especially k = 2 and k = 5)

- Multi-HD performance (high HD at short length and lower HD at long lengths)

- Effects of data values on coding effectiveness (applies only to checksums)

- Vulnerability to secondary effects (e.g., unprotected header with length; Controller Area Network (CAN) bit stuff issue)

- Synergy or conflict between error coding and bit encoding

- Computational cost: (speed, memory, recomputing after small dataword change)

- Polynomial divisibility by (x+1)

- Use of a primitive polynomial

- Use of published or standardized CRC

- Use of a polynomial with a specific factorization

- Error detection assessment given purely random corruption

- Detection of permutations in data order as the mode of corruption

## 2.2.3 Application Attributes.

- Configuration audit and configuration management (verifying version of installed software)

- Configuration data integrity check (e.g., message schedule, operating parameters in electrically erasable programmable read-only memory)

- Image integrity check for software update

- Boot-up integrity check of program image (e.g., flash memory)

- Random access memory (RAM) value integrity check

- Network packet integrity check

- Field-programmable gate array configuration integrity check

- Masquerade fault detection

- Implicit group membership check

## 2.2.4 Other Factors.

- Does system take credit for the following: (OK to have a small number of corrupted values [i.e., system inherently does not malfunction in response to a small number of corrupted values], acknowledgements, repetition, sequence numbers, other end-to-end mitigation strategies)

- Cryptographic authentication, secrecy, and/or integrity mechanisms

- Use of compression

- Temporal failures

- Propagation of message values through multiple paths

## 2.3 THE ADOPTED FAULT MODEL.

The fault model adopted for this work consisted of random independent bit errors, with a number of other factors addressed in the same context.

One way to evaluate error-detection performance is to consider unconstrained random data corruption. However, for this fault model, the choice of error-detection code is largely irrelevant. If essentially random data are being checked by an error-detection code, then one can expect a chance matching between dataword and k-bit FCS with probability  $1/(2^k)$ , regardless of the error coding approach (in essence, providing the performance of a random hash function as discussed in section 3.1, but due to data randomness rather than good hashing). As the number of faults in a codeword becomes small, there are very distinct differences between coding approaches. That is, the more bits that are corrupted, the less it matters which error-coding approach is used. However, if there are cases in which only a few bits might be in error, then the type of error code is relevant. Thus, selection should be focused on performance for only a few bits when that is a plausible data-corruption scenario. Performance with large numbers of bit errors can be expected to approach random hash performance with increasing numbers of bit errors.

For small numbers of bit errors, the HD of a code becomes relevant. Every code has specific patterns of relatively small numbers of bit errors that it cannot detect. Therefore, if the fault model is a specific pattern of bit errors, code performance depends on that specific pattern, which

is not generalizable. However, in most avionics cases, bit errors are not patterned, but are created by noise, random corruptions, or other mechanisms that can be considered random independent events. This random independent error event assumption is the fault model chosen. If a particular system has patterns of bit errors, such as those caused by hardware fault in an intermediate stage in a network, then the general results in this report may not apply.

The question arises as to how often random independent bit errors occur. Because this is a study of error detection rather than error correction, it must be assumed that any erroneous data must be discarded and that the emphasis is on maximizing the probability that data errors are detected. However, for any such system to work, the error rate must be relatively low or essentially all data will be discarded and the system will not perform any useful function. Therefore, it is reasonable for many applications to assume that the anticipated arrival of bit errors is, on average, significantly less than once per codeword (i.e., most codewords are error-free). This concept can be captured in a general way by considering bit errors to arrive via a Poisson process (exponential interarrival time) with a mean of a BER value that is significantly less than the inverse of the dataword size. For example, if codewords are 1000 bits long, the BER should be significantly less than 1/1000 to ensure that most codewords are error free. Given this approach, most codewords are error free, some contain 1-bit error, a few contain 2-bit errors, even fewer contain 3-bit errors, etc. This can be called a BER fault model (also known as a random independent binary symmetric bit inversion model).

As an approximation, the probability of r+1 bit errors occurring in a codeword is BER times the probability of r bit errors occurring. As a result, every bit of HD increase in an error-detection scheme results in an approximate factor of 1/BER reduction in the Pud. A more rigorous treatment of this idea follows.

The probability of an undetected error given a BER fault model depends on the following factors: the BER value, the size of the codeword, the HD of the error code being used, the Pud at the HD, and, in rare cases, the Pud at HD + 1. The Pud at the HD simply means the Pud given that HD bit errors have occurred.

Mathematically, this can be expressed (for a codeword having c bits) as:

$$Pud = Pud_{(HD)} + Pud_{(HD+1)}$$

(1)

Pud = combin(

$$c$$

, HD) \* UndetectedFraction<sub>HD</sub> \* BER<sup>HD</sup> \*  $(1 - BER)^{(c - HD)}$  + combin( $c$ , HD + 1) \* UndetectedFraction<sub>HD+1</sub> \*  $(BER^{(HD+1)} * (1 - BER)^{(c - HD+1)})$  (2)

In interpreting the first half of the equation, "combin()" is the number of combinations of the *c* bits of the codeword size taken one HD at a time, which is the total number of possible errors that can occur involving exactly the value of HD erroneous bits. The undetected fraction is the number of undetected errors out of all possible errors that involve HD bits, which varies depending upon the error detection code and how many error bits have been inserted (for a CRC, this is the HW divided by total number of possible errors; for other error-detection codes, the value used is typically the fraction of undetected errors found by a Monte Carlo simulation). The rest of the terms for HD involve the probability that exactly the value of HD bits are in error and

exactly (c-HD) bits are not in error. The second half of the right side of the equation repeats in a similar manner for HD + 1 error bits.

The Pud result is not affected by fewer than the value of HD errors because 100% of such errors are detected, based on the definition of HD. Terms involving HD + 2 and so on can be neglected because of the assumption that BER is small compared to the codeword size. The HD + 1 term only comes into play when a very small fraction of bit errors involving HD bits are undetected and the UndetectedFraction<sub>(HD + 1)</sub> is on the order of 1/BER or larger. For many cases, the HD + 1 term does not matter; the cases that do matter tend to be only at codeword lengths near the change of achieved HD, where there are only a few undetected errors having the new, lower HD number of bits in error. Based on this formulation of Pud, the dominant factors in error-detection effectiveness are the undetected error fraction and the HD, with each bit of HD giving an improvement in error detection effectiveness of an additional factor of approximately the BER. For example, with an undetected error fraction of 1.5e-6 (typical of a good 16-bit CRC), a BER of 1e-8, and HD = 4, each bit of HD accounts for almost two orders of magnitude more error detection effectiveness than the undetected error fraction. Thus, while the undetected error fraction is important to consider, for HD greater than 2 (depending on the quality of bit mixing in the error-detection code), HD is usually the dominant factor in achieved error-detection effectiveness. A more detailed example of how to apply these ideas is given in section 6.

Another common selection criterion is computational performance, with checksums often presumed to be calculated much faster than CRCs. However, research into CRC performance has not only produced fast CRC calculation techniques, but also CRC polynomials optimized for computation speed with only minimal reduction of error-detection effectiveness. A research report [3] provides further details. This report considers only error-detection effectiveness. If a checksum or quick-to-compute function provides sufficient error-detection effectiveness, then that may help with computation speed. However, computation speed should not be an excuse to accept inadequate error-detection capabilities.

The following sections describe the evaluation of checksums and CRC in terms of HD, undetected error fraction, and Pud given an assumed BER.

## 2.4 CHECKSUM EVALUATION.

Checksum error-detection effectiveness evaluation was performed via Monte Carlo simulation using the Mersenne Twister random number generator [4] as the source of pseudo-random numbers. The data array used by that generator was seeded with values from the Unix "random()" linear congruential generator, which was, in turn, seeded with date and time information.

Each trial was performed using the following steps:

1. Generate a random dataword value with an exact predetermined number of randomly positioned bits set to "1" with the rest set to "0."

- 2. Compute the checksum of this randomly generated dataword and append that FCS value to form a codeword.

- 3. Generate a random error vector with an exact predetermined number of randomly placed "1" error bits across the entire codeword, with "0" bits elsewhere in the error vector.

- 4. Compute the corrupted codeword by XORing the error vector into the codeword, resulting in bit flips where the error vector has "1" bits.

- 5. Determine if the resultant corrupted codeword was valid by computing the checksum of the corrupted dataword and comparing that result to see if it matches the corrupted FCS from the codeword.

- 6. Record an undetected error if the corrupted codeword was valid (because this means that the corrupted dataword corresponds to the corrupted FCS, resulting in a valid corrupted codeword and, therefore, an undetected error).

Note that the trial procedure differs from simply generating unconstrained random dataword values in that an exact number of desired bits are set in the dataword for every trial (e.g., exactly 50% "1" bits), rather than that number of bits being set on average with some distribution of actual numbers of one bits. Therefore, if 50% of bits are supposed to be 1 bits for a 128-bit dataword, then exactly 64 randomly positioned bits are 1 for each and every trial. Additionally, error bits affect the entire codeword, including dataword, the FCS bits, or both, depending on the error bit placement in a particular trial.

Multiple trials were performed per data point, with a data point being a particular number of error bits and a particular dataword length of interest. Except where noted elsewhere, each data point had enough trials run to experience at least 500 undetected errors for every data point that was used to graph results (and, for all but the longest datawords examined, at least 1000 undetected errors were seen). After confirming that a 50% mix of ones and zeros results in worst case undetected error fractions for checksums [5], datawords with 50% randomly positioned one bit sets were used for all reported Monte Carlo experiments.

Determining the transition point between HD values was difficult because of the need to use random sampling rather than exhaustive enumeration (exhaustive enumeration is impracticable because there are too many possible combinations of dataword values and bit error patterns to consider). Thus, the transition point from one HD to another was estimated using a general approach of finding dataword lengths straddling the point at which undetected errors suddenly disappear for a given sample size. This approach is useful because, based on experimental data, the proportion of error patterns that is undetected varies only slightly as dataword length increases. The transition between HD = 4 and HD = 3 serves as an example. The HD = 3 results (undetected 3-bit errors) were readily found for ATN-32 down to a dataword length of 4064 bits. At that length, a large number of trials were used to evaluate the ATN-32 checksum at a dataword length of 4064 bits with exactly 2032 dataword bits set to "1" and exactly 3 error bits set in each trial. Enough trials were run to find approximately 1000 undetected 3-bit errors, confirming HD = 3 at that dataword length. More precisely, 9.95e11 trials resulted in the

discovery of 1064 undetected errors. This same experiment was repeated for the next shorter considered dataword length of 4032 bits (which is one 32-bit word shorter than 4064 bits). At that slightly shorter length, approximately the same number of trials were run (1.01e12 trials), without discovering any undetected 3-bit errors, suggesting HD = 4. While it is always possible that there is still some undetected 3-bit error pattern at this dataword length of 4032 bits, one expects that the density of such undetected error patterns must be dramatically lower than the density of undetected errors at 4064 bits. If the normal behavior of nearby HD = 3 dataword lengths having a similar proportion of undetected 3-bit error patterns held, one would expect to find hundreds of undetected errors at a dataword length of 4032 bits, rather than zero such undetected errors. Put another way, consider two neighboring dataword lengths. The slightly longer one has about 1000 undetected 3-bit errors, while the slightly shorter one has zero undetected 3-bit errors for a comparable number of random trials. Based on that, it is very likely that the boundary between HD = 3 and HD = 4 lies between those two dataword lengths (4-bit undetected errors were identified with a separate set of experiments at a dataword length of 4032 bits, confirming that HD = 4 rather than some higher HD).

While it is tempting to apply statistical analysis to give a confidence interval to these simulation results, the reality is either that there are or are not one or more undetectable 3-bit errors at that length; stochastic simulation either will or will not find one of them. The statistical significance would apply to whether the simulation result of no undetected errors might be correct, but that is not the same as yielding the Pud that would be needed as part of a safety case. It would address the question as to whether the HD is likely to be correct, but it is unclear how to use that number in computing Pud. Given that the ratio of undetected errors is approximately 1 in every 1e9 corrupted codewords for 4064 bits (and less for 4032 bits), it would be easy to miss undetected errors even if a statistical analysis was performed.

One could assume that undetected errors are present even if not found via nonexhaustive simulation, and could apply statistical analysis to estimate the Pud at the HD of bit errors that have not been found, but might possibly be present. That approach is used in an informal manner in section 3.8 when analyzing the ATN-32 HD thresholds. However, coming up with a usable probability requires careful statistical evaluation that is beyond the scope of this report. One factor to consider is that patterns that are undetected by checksums and CRCs are a combination of both pseudo-random error patterns and repeating error patterns. For example, in a checksum with all zero or all one dataword values, an error pattern that consists of only dataword bit flips will be found to occur multiple times as an identical bit pattern starting at every possible dataword position. This is because dataword-only undetected errors are self-contained error patterns in which the contributions of earlier error bits to the checksum calculation are cancelled-out by later error bits, leading to a zero contribution to the final FCS value. This cancellation effect happens regardless of the positioning of the error pattern within the dataword, as long as it does not spill into the FCS region. For example, if a particular error pattern involving 100 dataword bits (and no FCS bits) is undetectable, then a 1000-bit dataword will have 900 such identical patterns of undetected errors, starting at 900 different dataword positions (i.e., the 100-bit undetected error pattern starting at the first bit, that same pattern starting at the second bit, then starting at the third bit, etc. until starting at the 900th bit, after which the error pattern would spill into the FCS and, in most cases, would then be detectable). Thus, any

statistical analysis would have to consider the effect of nonrandom distributions of undetected error patterns, which may or may not matter (a similar effect occurs with CRCs, but in that case is independent of dataword values). Moreover, the result would have a statistical confidence level as to the Pud value at not just the presumed HD, but for all numbers of bit errors for which an exhaustive search has not been performed (e.g., if an exhaustive search for 3-bit errors has not been performed, then HD = 3 must be assumed to be true with some Puds even though no cases of undetected 3-bit, 4-bit, or 5-bit errors have been found). Any such confidence levels would have to be taken into account in any system-level analysis. Given that exhaustive searches for checksums require consideration of all possible dataword values as well as all possible error patterns, simulation is generally unsuitable to make definitive statements about HD beyond any HD that can be argued analytically. Thus, both Pud values and HD values based solely on simulations are subject to some level of inaccuracy (CRC performance values for both HD and Pud given in this report are analytically exact, because they consider all possible error patterns and are independent of dataword values).

Returning to the discussion of ATN-32 performance, it seems unlikely (in a difficult-to-quantify sense) that the HD = 4 length is shorter than 4032 bits, especially if one looks at the characteristic downward curves in the plots just above that length (each point forming the curve right at the HD break point is based on 271–622 undetected errors, thus providing a reasonable degree of certainty as to the plotted values). In the absence of an analytic proof of HD characteristics of ATN-32, relying upon HD = 4 performance at dataword lengths up to and perhaps including 4032 bits could be reasonable, depending on the context.

Similar processes were used for other checksums and other lengths, with all other HD breakpoints having at least 1000 undetected errors' worth of trials. There is no analytically exact evaluation method available because checksum performance not only depends upon the error detection computation and the bits in error, but also the data values in the message.

Validity of the checksum computations was checked via comparison to a previous publication [5], which in turn was checked via comparison to known published results. There are no known published results for ATN-32 error-detection capabilities. Therefore, those results should be checked by an independent researcher.

It is possible that, in some applications, purely random dataword values are not representative. That is why the worst case of a 50% mix of ones and zeros is used. There may be specific data value patterns that are even worse because of the particular arrangement of ones and zeros. However, whether or not the difference is significant is not known. Such patterns could potentially change the undetected error fraction, but would not be expected to make the HD worse.

## 2.5 THE CRC EVALUATION.

The CRC error-detection performance was evaluated using analytically exact exhaustive analyses of all possible k-bit codeword error patterns (i.e., for evaluating performance with k error bits). The CRC HWs are independent of the dataword values, meaning that dataword values do not matter in this evaluation. The approaches described in references 2 and 6 were used for this

analysis. The outputs of the CRC evaluation tool have previously been extensively checked for validity against a wide variety of other CRC error-detection publications.

## 2.6 OTHER EVALUATIONS.

Evaluations of other specific error-detection technique combinations were done via Monte Carlo analysis, including evaluation of multi-CRC approaches, such as used in Aeronautical Radio, Incorporated (ARINC)-825. There are no known publications for comparison of the other results. However, in some cases, it is straightforward to argue why a particular HD result is valid.

## 3. CHECKSUM AND CRC ERROR DETECTION.

The error detection performance of checksums depends on how well the checksum computation mixes the bits of data to form an FCS value and whether that mixture is done in such a way that a particular HD is guaranteed for every possible error pattern below that HD value. Sections 3.1 through 3.9 describe error-detection performance for a variety of checksum and CRC approaches.

## 3.1 RANDOM HASH HD = 1 ERROR DETECTION.

Summary:

Quasi-random mixing function with HD = 1 (e.g., a cryptographically secure hash function)

HD = 1

Undetected Error Fraction at HD:  $1/(2^k)$  for k-bit FCS

Burst Error Coverage: None

Is it Data Dependent?: Theoretically; however, mixing quality is independent of data Does it Detect Change in Data Order?: Yes, subject to HD and undetected error fraction

This is an abstract approach to describing checksum and CRC error-detection performance. The assumption is that some checksum-like function has been defined, which provides excellent mixing of bits in computing a checksum, but it misses detection of some 1-bit errors. In this case HD=1, but because of the assumption of perfectly random mixing, a change in any 1 bit of the dataword changes each bit of the checksum with an equal and completely random probability. In such a system, it is possible that a 1-bit error in a dataword will have no effect on the FCS value (if HDs higher than 1 were guaranteed, that property would form a predictable pattern in the output of the mixing function, leading, at least theoretically, to a security vulnerability). For this function, the undetected error fraction of 1-bit errors is  $1/(2^k)$  for a k-bit FCS. In general, there would be no guarantee of burst error detection coverage because a 1-bit error in the wrong situation may be undetected. It must be emphasized that this is a theoretical limit rather than a finding that applies to any particular hash function. Table 1 shows the theoretical performance of a random hash function.

Table 1. Random Hash Error Detection

|                        | Analytic           |

|------------------------|--------------------|

| Checksum Size          | Undetected         |

| Dataword Length = 1024 | Fraction at HD = 1 |

| 8-bit hash             | 0.00391            |

| 16-bit hash            | 1.53e-5            |

| 32-bit hash            | 2.33e-10           |

In practice, cryptographically secure hash functions are likely to provide this type of error detection because they are not designed to provide a certain HD, but instead cryptographically secure mixing of bit values.

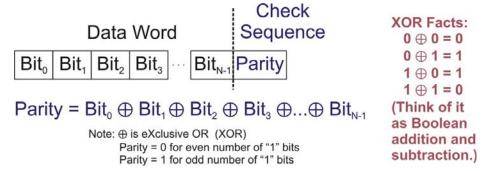

## 3.2 PARITY.

Summary:

Single parity bit added to dataword

HD = 2

Undetected Error Fraction at HD: 100% within a dataword

Burst Error Coverage: None Is it Data Dependent?: No

Does it Detect Change in Data Order?: No

Single-bit parity is computed by XORing all the bits of a dataword to form one single parity bit. That bit is a zero if the number of "1" bits in the dataword is even, and is a one if the number of "1" bits in the dataword is odd (some systems invert the sense of the parity bit so that an all zero dataword has a parity value of 1, avoiding the possibility of an all zero codeword).

Per-word parity gives HD = 2 on a per-dataword basis with no burst error detection. Any 2-bit errors in a dataword plus parity data set are undetected and performance is insensitive to data values. Because it is a per-word error code, each word has error detection independent from other words. It also costs one extra bit per dataword, making it more expensive in terms of bits than other error codes for all but the shortest datawords.

All even-number bit errors are undetected by parity, so the undetected error fraction at HD = 2 is 100% within a dataword. When considering a multiword message, the analysis depends on data length. However, the general outcome is that, for an error to be undetected, all words must either be error-free or have an even number of errors (see section 4.1 for a case study). Thus, the undetected error fraction is less than 100% for 4-bit errors and other higher-order even numbers of bit errors because of the decreasing probability that all errors will be allocated in pairs to words of a multiword message.

#### 3.3 LONGITUDINAL REDUNDANCY CHECK.

Summary:

Block-wise XOR of all data blocks

HD = 2

Undetected Error Fraction at HD: 3.125% for 32-bit chunk size at all dataword lengths

Burst Error Coverage: Chunk size

Is it Data Dependent?: No

Does it Detect Change in Data Order?: No

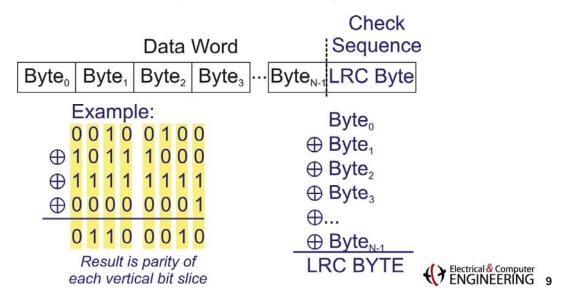

A longitudinal redundancy check (LRC), also known as an XOR checksum, involves XORing all the chunks of a dataword together to create a check sequence. It is equivalent to computing the parity of each bit position within a chunk independently (i.e., check sequence position i is the parity of bit position i across all chunks in the dataword). There is no obvious seminal publication for LRC, but it is referred to frequently in the checksum literature.

The LRC error codes give HD = 2, with burst error detection up to the chunk size. Any 2-bit errors in the same bit position of a block (including the FCS) are undetected, and error detection performance is insensitive to data values. If any bit position has an odd number of bit errors, the LRC will detect that there is an error, improving average case performance compared to a single parity bit. An LRC can be thought of as computing a separate parity bit for each bit position of the block, and saving those parity bits as an FCS. An error is detected unless every one of those parity bits fails to detect all errors in that bit position.

The probability of an undetected 2-bit error for LRC depends on the computation chunk size. Conceptually, it is the probability that the 2-bit errors happen to align in the same bit position of the chunk (e.g., for an 8-bit chunk with one error in bit 3 of the chunk, the second error has to be in bit 3 of some other chunk for the FCS to be undetected).

As per Maxino and Koopman [5], the probability of an undetected 2-bit error is:

$$\frac{n-k}{k(n-1)}\tag{3}$$

In this equation, k is the number of FCS bits, and n is the number of codeword bits. Undetected error probabilities from Monte Carlo Simulation with a 1024-bit dataword are given in table 2, with the analytic values from the Maxino equation.

Table 2. The LRC Error Detection

| Checksum Size   | Simulated            | Analytic             | Difference  |

|-----------------|----------------------|----------------------|-------------|

| Dataword Length | Undetected           | Undetected           | From        |

| = 1024          | Fraction at $HD = 2$ | Fraction at $HD = 2$ | Analytic    |

| 8-bit LRC       | 0.12417              | 0.12415              | 0.01% worse |

| 16-bit LRC      | 0.06160              | 0.06160              | 0.00%       |

| 32-bit LRC      | 0.03032              | 0.03033              | 0.04% worse |

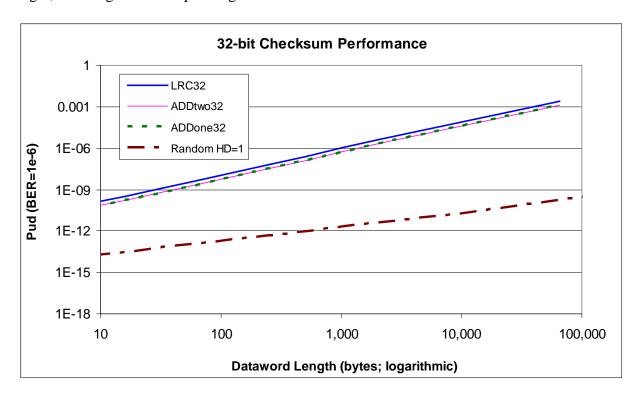

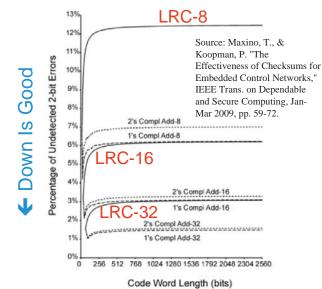

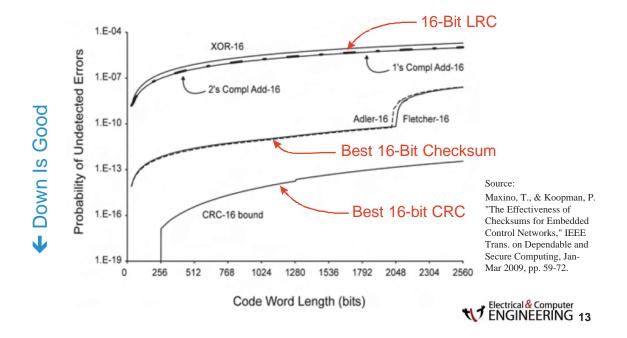

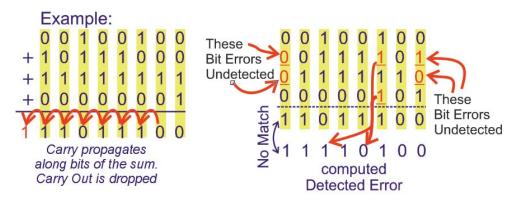

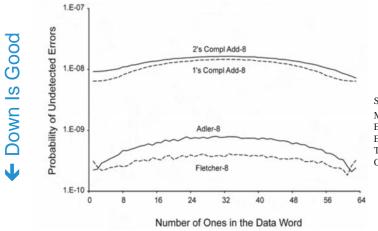

Figure 1 shows simulation results for a 32-bit LRC and other checksums on a log-log plot, with dataword lengths in bytes. Plots for 8-bit and 16-bit checksums are similar. While the undetected error fraction is constant, the probability of multibit errors increases with dataword length, resulting in a corresponding increase in Pud.

Figure 1. The Pud for LRC and Addition Checksums (downward means better Pud)

Of note in figure 1, an HD = 1 random hash value does better than an HD = 2 checksum. This is because the undetected error fraction of the checksums shown is quite high, due to relatively poor bit mixing by the checksum functions. In other words, a good hash function with HD = 1 can be expected to do better than one of these checksums with HD = 2 (however, other checksums and CRCs can do much better than the checksums shown in this figure).

When plotting error-detection performance, as in figure 1, it is important to be mindful of the assumed BER. The values plotted will depend heavily upon that value. Additionally, it is in most cases meaningless to extend the graph past the point at which every message is likely to

have an error; the system using error detection codes will throw away essentially all of its data as erroneous. In the case of figure 1, the longest length plotted is 100,000 bytes = 800,000 bits, which is close to BER = one error per 1,000,000 bits.

## 3.4 TWO'S COMPLEMENT CHECKSUM.

Summary:

Normal integer addition of all data blocks

HD = 2

Undetected Error Fraction at HD: 1.565% for 32-bit FCS

Burst Error Coverage: Chunk size

Is it Data Dependent?: Yes

Does it Detect Change in Data Order?: No

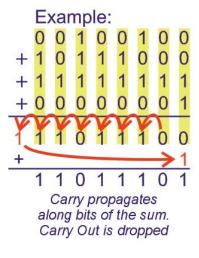

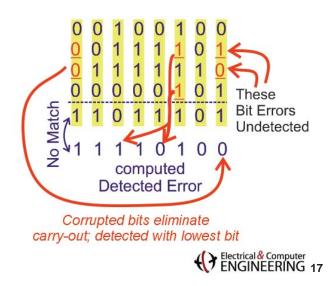

Checksums are computed by using integer addition of all chunks of a dataword, with the resultant sum forming the check sequence. As with parity-based computations, it is difficult to define a seminal publication for two's complement addition checksums.

A two's complement checksum gives HD = 2 with burst error detection up to the chunk size. It operates by using normal (two's complement) addition instructions. The number of 2-bit errors that are undetected is reduced compared to an LRC error code because a pair of inverted bits in the same bit position can sometimes be detected by the fact that the carry generated by adding those bits is different. However, reliance on carry operations to improve checksum effectiveness means that the performance is data dependent, with performance best at either all zero or all one dataword values and worst with a random 50% mix of one and zero dataword values.

As is typical for two's complement computer arithmetic, carry-outs from the highest bit of the addition are ignored, making the top bit of each block more vulnerable to undetected errors (all bits in the block are protected by the carries from an addition operation, but the topmost bit in the block is protected only by an LRC operation due to throwing away the carry-out from the topmost bit addition).

The analytic undetected error fraction is complex, but a simplified approximation that is most accurate at long dataword lengths and pessimistic at short data lengths is given by Maxino and Koopman [5]:

$$\frac{k+1}{2k^2} \tag{4}$$

Table 3 shows two's complement error-detection performance. Figure 1 shows that a two's complement checksum is significantly better than an LRC due to the internal carry bits reducing the probability of undetected 2-bit errors. However, the significant amount (approximately a factor of two) is still relatively small on a log-log scale.

Table 3. Two's Complement Checksum Error Detection

|                   |                      | Published Undetected Fraction Approximation at |            |

|-------------------|----------------------|------------------------------------------------|------------|

| Checksum Size     | Simulated            | HD = 2 [5]                                     |            |

| Dataword length = | Undetected           | (valid for all                                 |            |

| 1024              | Fraction at $HD = 2$ | lengths)                                       | Difference |

| 8-bit chk2        | 0.06990              | 0.07031                                        | 0.59%      |

| 16-bit chk2       | 0.03275              | 0.03320                                        | 1.36%      |

| 32-bit chk2       | 0.01565              | 0.01611                                        | 2.86%      |

## 3.5 ONE'S COMPLEMENT CHECKSUM.

Summary:

One's complement integer addition of all data blocks

HD = 2

Undetected Error Fraction at HD: 1.518% for 32-bit FCS

Burst Error Coverage: Chunk size

Is it Data Dependent?: Yes

Does it Detect Change in Data Order?: No

In terms of the mechanics of computation, a one's complement addition is the same as a two's complement addition, except that in the case of the one's complement, the carry-out of each addition is added back into the lowest bit position of that addition result. In other words, if a two's complement addition results in a carry-out of zero, then that is used as the one's complement addition result. However, if a two's complement addition results in a carry-out of one, then the addition result is incremented by one to give a one's complement addition result. This is an implementation method that correctly deals with the fact that an all zero bit pattern and an all one bit pattern both represent the number zero in one's complement arithmetic.

From an error-detection point of view, the benefit of this computational approach is that carry-out bits are captured during the computation instead of being thrown away, slightly increasing bit mixing and error detection effectiveness. Usas provided analysis demonstrating the superiority of one's complement addition to two's complement addition [7].

The analytic undetected error fraction is complex, but as simplified approximation for long data lengths is given as in Maxino and Koopman [5]:

$$\frac{1}{2k} \tag{5}$$

Table 4 shows one's complement error detection performance. Figure 1 shows that, whereas a one's complement checksum provides slightly better error detection than a two's complement checksum, the difference is difficult to see on a log—log plot. If possible, a one's complement checksum should be used rather than a two's complement checksum. However, it is better to use a more advanced checksum, such as a Fletcher checksum.

Table 4. One's Complement Checksum Error Detection

| Checksum Size   | Simulated            |                               |            |

|-----------------|----------------------|-------------------------------|------------|

| Dataword length | Undetected           | Published Undetected Fraction |            |

| = 1024          | Fraction at $HD = 2$ | Approximation at $HD = 2$ [5] | Difference |

| 8-bit chk1      | 0.06214              | 0.06250                       | 0.58%      |

| 16-bit chk1     | 0.03083              | 0.03125                       | 1.34%      |

| 32-bit chk1     | 0.01518              | 0.01563                       | 2.86%      |

## 3.6 FLETCHER CHECKSUM.

## Summary:

One's complement integer addition of two running sums

HD = 3 for short lengths; HD = 2 for longer lengths

Burst Error Coverage: At least half of FCS size (i.e., size of one running sum)

Is it Data Dependent?: Yes

Does it Detect Change in Data Order: Yes, subject to HD and undetected error fraction

The Fletcher checksum [8] is computed with a pair of running arithmetic sums. The first running sum is simply the one's complement sum of all chunks in the dataword. The first running sum is added into the second running sum after every data chunk is processed:

$$SumA = SumA + next data chunk$$

(6)

$$SumB = SumB + SumA \tag{7}$$

Both *SumA* and *SumB* are initialized to some constant value. The additions are one's complement addition and the process is iterated over data chunks for the entire dataword with the data chunk size being half of the FCS size. At the end of the checksum computation, the FCS is the concatenation of *SumA* and *SumB*. Thus, a 32-bit Fletcher checksum is the concatenation of a 16-bit *SumA* value and a 16-bit *SumB* value. This iterative approach leaves the second sum with one times the last data chunk, two times the next-to-last data chunk, three times the next-most-recent data chunk, etc. This makes it possible to detect changes in data order for HD = 3 error-detection lengths. Fletcher checksums use one's complement addition as previously described for a one's complement checksum.

Nakassis [9] provides implementation hints for the Fletcher checksum and provides error detection effectiveness metrics based on probability of undetected random corruption, 16-bit burst errors, single-bit errors, and minimum distance between undetected double-bit errors. The

incorrect use of two's complement addition instead of one's complement addition for computing a Fletcher checksum is shown to reduce the minimum distance between undetected double-bit errors from 2040 bits distance for a 16-bit Fletcher checksum (two 8-bit chunks) to only 16 bits distance. Nakassis also suggests a metric of ease of recomputing a checksum after a small change to the dataword and suggests that the Fletcher checksum is better according to that metric.

An 8-bit Fletcher Checksum has HD = 3 up to 60 dataword bits and HD = 2 above that, which this report has confirmed [5]. A 16-bit Fletcher checksum is HD = 3 up to 2039 bits, which this report has confirmed. Maxino and Koopman [5] similarly projected HD = 3 up to 1,048,559 bits, which this report has found to be incorrect after extensive simulation. No 2-bit undetected error was found at that length with 1e8 trials of Monte Carlo simulation, which run quite slowly because of the large data structures involved. However, based on the patterns of Fletcher checksum computation, there is reason to believe such a pattern exists and the predicted HD = 2 dataword length. However, it could take well in excess of 1e9 trials to detect one, which would exceed the time available given fixed computational resources.

One way to look at the Fletcher checksum performance pattern is to consider that the running sums are half the FCS size. In those terms, an 8-bit Fletcher checksum has HD = 2 performance starting at just over 15 dataword blocks of 4 bits. A 16-bit Fletcher checksum has HD = 2 performance starting at 255 dataword blocks of 8 bits and a 32-bit Fletcher checksum has HD = 2 performance starting at 65,535 dataword blocks of 16 bits.

Table 5 shows that Fletcher checksums achieve a better HD than addition checksums up to a certain length determined by the size of the Fletcher checksum.

Table 5. Fletcher Checksum Error Detection

| Checks           | sum Size       | Simulated Undetected<br>Fraction of 2-Bit Errors | Simulated Undetected<br>Fraction of 3-Bit Errors  |

|------------------|----------------|--------------------------------------------------|---------------------------------------------------|

| 8-bit Fletcher:  | (56 bits)      | 0                                                | 0.00388                                           |

|                  | (64 bits)      | 0.00153                                          | 0.00381                                           |

|                  | (1024 bits)    | 0.00780                                          | 0.00317                                           |

| 16-bit Fletcher: | (1024 bits)    | 0                                                | 5.28e-5                                           |

|                  | (2032 bits)    | 0                                                | 4.76e-5                                           |

|                  | (2048 bits)    | 3.76e-6                                          | 4.81e-5                                           |

| 32-bit Fletcher: | (1024 bits)    | 0                                                | 2.77e-5                                           |

|                  | (65536 bits)   | 0                                                | 3.35e-7                                           |

|                  | (1048544 bits) | Should be 0                                      | >0 (insufficient samples to provide exact number) |

|                  | (1048576 bits) | >0(none found)                                   | >0<br>(not measured)                              |

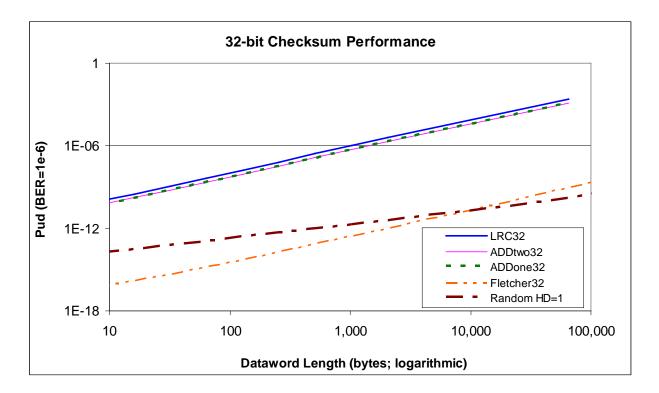

Figure 2 shows that Fletcher checksum performance is significantly better than other checksums discussed and has good enough mixing properties that it is better than a random hash for all short-to-medium dataword lengths (up to approximately 8 kilobytes [Kbytes]), but worse for long dataword lengths. This is because the addition operation gives the Fletcher checksum only mediocre mixing. It has HD = 3 instead of HD = 2 performance at those lengths and the extra bit of HD makes up for the poor mixing for this BER value. Note that in this report figures show dataword lengths in bytes and tables show dataword lengths in bits.

Figure 2. The 32-Bit Checksum Performance

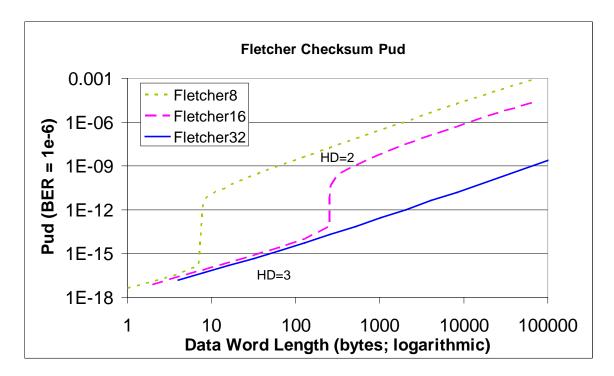

Figure 3 shows a comparison of 8-bit, 16-bit, and 32-bit Fletcher checksum performance. The dramatic decreases in Pud for the 8-bit and 16-bit curves correspond to the places where they degrade from HD = 3 to HD = 2 performance. This change is significantly larger than the distance between curves where they have the same HD, emphasizing the importance of HD in error detection given a BER fault model.

Figure 3. Fletcher Checksum Performance

## 3.7 ADLER CHECKSUM.

The Adler checksum [10] is the same as a Fletcher checksum, except Adler checksums use modulo addition. The modulus chosen is the largest prime number smaller than the relevant power of 2 for the chunk size being added. In practice, this means an 8-bit chunk size is added modulo 251 (i.e., using a modulus of 251), and a 16-bit chunk size is added modulo 65,521.

The use of a prime modulus provides better mixing of bits, but comes at the cost of having fewer valid check sequence values. This is because some FCS values are never generated because of the modular division. For example, with an 8-bit chunk size, the values 251, 252, 253, 254, and 255 are invalid under the modulus of 251 and, therefore, cannot appear in either byte of the 16-bit check sequence, giving fewer possible check sequence values and slightly increasing the probability of a multi-bit error creating a valid codeword randomly. The tradeoff of better mixing with a prime modulus versus fewer possible check sequence values was studied [5]. In general, an Adler checksum usually is worse than a Fletcher checksum and only improves error detection by a slight amount in the regions where it is better. Because of the more expensive computation required, this checksum was not studied further and, in general, is not recommended as a worthwhile tradeoff. Given the computational complexity required, a CRC should be used instead of an Adler checksum.

## 3.8 THE ATN-32.

Summary:

ATN-32 modified Fletcher checksum

HD = 3, 4, or 6 for shorter lengths

HD = 2 for long lengths

Burst Error Coverage: At least one quarter chunk size

Is it Data Dependent?: Yes

Does it Detect Change in Data Order?: Yes, subject to HD and undetected error fraction

The ATN-32 checksum can be thought of as a modified Fletcher checksum that uses four running one's complement sums of 8 bits each to create a 32-bit checksum value [11]. The final value is a computational mixture of the four running sums rather than a simple concatenation, as shown in figure 4 (a reproduction of figure 6.25 of reference 11).

The ATN message checksum shall be generated by the following algorithm:

- a) Initialize C0, C1, C2 and C3 to zero.

- b) Process each octet in the message sequentially from i = 1 to L by:

- 1) adding the value of the octet to C0; and

- 2) then adding the value of C0 to C1, C1 to C2, and C2 to C3.

- c) Set the octets of the checksum as follows:

- 1) X0 = -(C0 + C1 + C2 + C3);

- 2) X1 = C1 + 2\*C2 + 3\*C3;

- 3) X2 = -(C2 + 3\*C3); and

- 4)  $X_3 = C3$ .

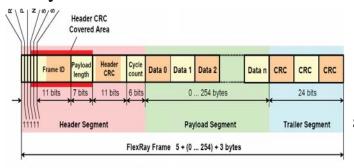

Figure 4. The ATN-32 Checksum Algorithm [11]

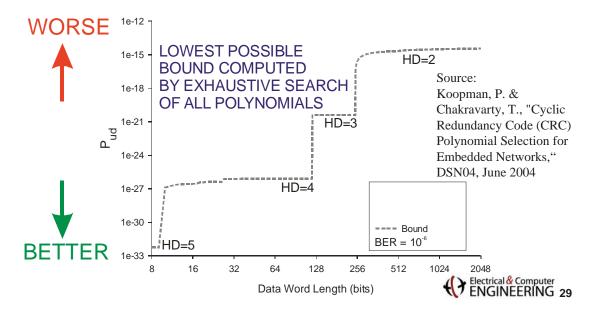

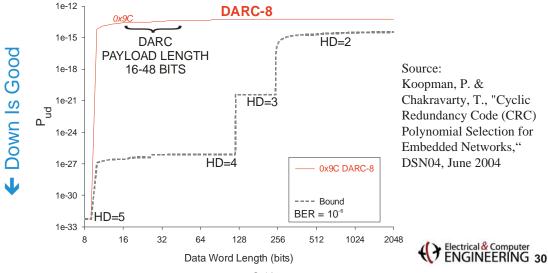

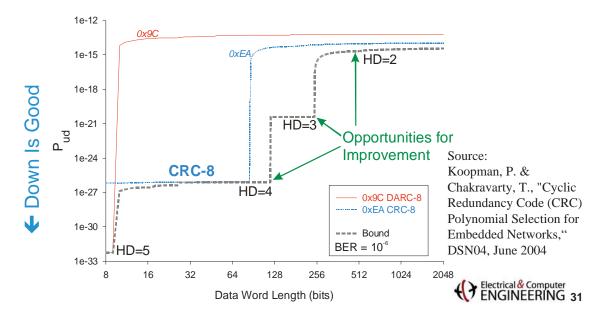

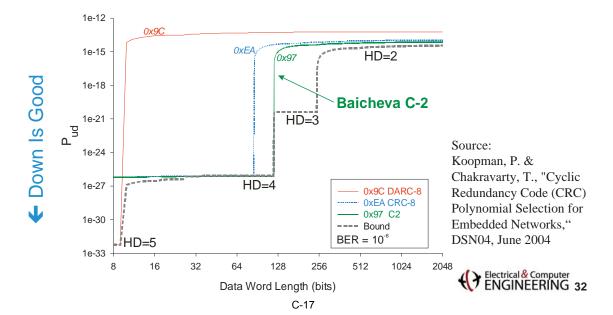

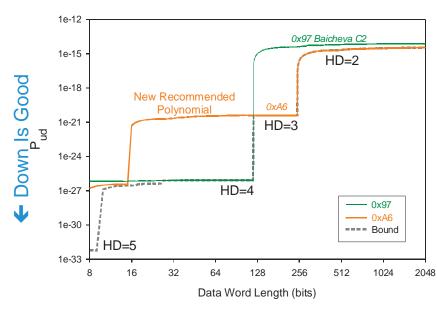

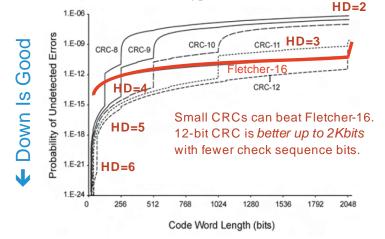

Error detection effectiveness of the ATN-32 checksum is shown below. It has HD = 6 up to 96-bit datawords, HD = 4 up to 4032-bit datawords, and HD = 3 up to 6080-bit datawords. At and beyond 6112 bit datawords, it has HD = 2. This gives an additional bit of HD up to 4032 bits compared to a conventional Fletcher checksum, but, as a tradeoff, degrades to HD = 2 at only 6112 bits.