#### DOT/FAA/AR-11/2

Air Traffic Organization NextGen & Operations Planning Office of Research and Technology Development Washington, DC 20591

# Handbook for the Selection and Evaluation of Microprocessors for Airborne Systems

February 2011

Final Report

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

U.S. Department of Transportation Federal Aviation Administration

#### **NOTICE**

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The United States Government assumes no liability for the contents or use thereof. The United States Government does not endorse products or manufacturers. Trade or manufacturer's names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA certification policy. Consult your local FAA aircraft certification office as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: actlibrary.tc.faa.gov in Adobe Acrobat portable document format (PDF).

**Technical Report Documentation Page**

|                                                                                                                                                                                                          | <u>.</u>                                                                                       | Technical Report Documentation Page   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------|

| 1. Report No.<br>DOT/FAA/AR-11/2                                                                                                                                                                         | 2. Government Accession No.                                                                    | 3. Recipient's Catalog No.            |

| Title and Subtitle                                                                                                                                                                                       | 5. Report Date                                                                                 |                                       |

| HANDBOOK FOR THE SELECTION A                                                                                                                                                                             | February 2011                                                                                  |                                       |

| MICROPROCESSORS FOR AIRBORN                                                                                                                                                                              | 6. Performing Organization Code                                                                |                                       |

| 7. Author(s)  Bob Green <sup>1,</sup> Joseph Marotta <sup>2</sup> , Brian Pet Gupta <sup>6</sup> , Daniel O'Leary <sup>7</sup> , Jason Dan Lo Manners <sup>9</sup> , and Dr. Rabi Mahapatra <sup>6</sup> | Performing Organization Report No.                                                             |                                       |

| 9. Performing Organization Name and Address  BAE Systems 600 Main Street Johnson City, NY 13790                                                                                                          | <sup>2</sup> Honeywell Aerospace<br>9201 San Mateo, Blvd., NE, MS C01<br>Albuquerque, NM 87113 | 10. Work Unit No. (TRAIS)             |

| <sup>3</sup> GE Aviation <sup>4</sup> Hamilton Sundstrand Corporation 3290 Patterson Ave., SE Grand Rapids, MI 49512-1991  Windsor Locks, CT 06096                                                       |                                                                                                |                                       |

| <sup>5</sup> Federal Aviation Administration Technical Programs and Continued Airworthiness Branch, AIR-120 Washington, D.C. 20024 <sup>6</sup> Texas A&M University College Station, TX 77845           |                                                                                                |                                       |

| <sup>7</sup> Lockheed Martin                                                                                                                                                                             | <sup>8</sup> Boeing                                                                            |                                       |

| PO Box 745, MZ8667                                                                                                                                                                                       | PO Box 3707                                                                                    |                                       |

| Ft. Worth, TX 76101                                                                                                                                                                                      | Seattle, WA 98124                                                                              |                                       |

| <sup>9</sup> Lumark Technologies, Inc.                                                                                                                                                                   |                                                                                                |                                       |

| 4904 Tydfil Court, Ste 100                                                                                                                                                                               |                                                                                                | 11. Contract or Grant No.             |

| Fairfax, Virginia 22030                                                                                                                                                                                  |                                                                                                |                                       |

| 12. Sponsoring Agency Name and Address                                                                                                                                                                   |                                                                                                | 13. Type of Report and Period Covered |

| U.S. Department of Transportation                                                                                                                                                                        | Final Report                                                                                   |                                       |

| Federal Aviation Administration                                                                                                                                                                          |                                                                                                |                                       |

| Air Traffic Organization NextGen & Ope                                                                                                                                                                   |                                                                                                |                                       |

| Office of Research and Technology Deve                                                                                                                                                                   |                                                                                                |                                       |

| Washington, DC 20591                                                                                                                                                                                     | 14. Sponsoring Agency Code                                                                     |                                       |

|                                                                                                                                                                                                          | AIR-120                                                                                        |                                       |

| 45 0 1 4 11 4                                                                                                                                                                                            |                                                                                                | ·                                     |

15. Supplementary Notes

The Federal Aviation Administration Airport and Aircraft Safety R&D Division COTR was Charles Kilgore.

Abstrac

This Handbook provides research information intended to help aerospace system developers and integrators and regulatory agency personnel in the selection and evaluation of commercial off-the-shelf microprocessors for use in aircraft systems.

This Handbook is based on the cooperative research accomplished by contributing members of the aerospace industry and the Federal Aviation Administration (FAA) as part of the Aerospace Vehicle Systems Institute Microprocessor Evaluations Projects 1 through 5. The project objectives were to (1) identify common risks of using systems-on-a-chip (SoC) and mitigation techniques to provide evidence that they satisfy regulatory requirements and (2) evaluate existing regulatory policy and guidelines against the emerging characteristics of complex, nondeterministic microprocessors and SoCs to support the certification of aircraft and qualification of systems using these devices.

Complex aircraft system development requires more robust consideration of system failure and anomaly detection, correction, and recovery. The safety net approach identified in this Handbook also may provide a means to reduce the growing difficulties and costs of design assurance for highly integrated, complex, nondeterministic airborne electronic hardware and software within aircraft systems and reduce the labor burden for FAA regulation compliance and design assurance. The safety net approach documented in this Handbook is consistent with current FAA policy and guidelines.

Microprocessor, System-on-a-chip, Safety net, Aircraft certification, System qualification, Airborne electronic hardware, Aircraft safety, System architecture, Simulation, Operational level error detection and recovery, Integrated circuits, Avionics safety, Architecture patterns

18. Distribution Statement

This document is available to the U.S. public through the National Technical Information Service (NTIS), Springfield, Virginia 22161. This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

19. Security Classif. (of this report)

20. Security Classif. (of this page)

21. No. of Pages

22. Price

Unclassified

60

#### **ACKNOWLEDGEMENTS**

The authors would like to thank the following people for their direct contributions to this Handbook and their persistent efforts throughout the course of this project:

- Floyd Fazi, Lockheed Martin

- Bob Green, BAE Systems

- Nikhil Gupta, Texas A&M University

- Charles Kilgore, FAA

- Jason Lee, Texas A&M University

- Kirk Lillestolen, Hamilton Sundstrand

- Rabi Mahapatra, Texas A&M University

- Bob Manners, Lumark Technologies, Inc.

- Joseph Marotta, Honeywell

- Arnold Nordsieck, Boeing

- Daniel O'Leary, Lockheed Martin

- Brian Petre, GE Aviation

- Richard Spencer, FAA

- John Strasburger, FAA

The authors acknowledge the following individuals and organizations for providing support to the creation of this Handbook:

- Praveen Bhojwani, Texas A&M University

- Amita Biswas, Texas A&M University

- Luis Bonet, Glenn Beck, John McLellan, and John Abrams, Freescale Semiconductor

- David Beal, Chris Hall, Chad Margolin, and Jakob Engblom, Virtutech, Inc.

- Bob Chobot, BAE Systems

- Rob Clements, BAE Systems

- Robert Cox, Hamilton Sundstrand

- Wolfgang Denk, DENX Software Engineering

- Kyle Deutsch, BAE Systems

- Jon Diekama, GE Aviation

- Chris Eckert, GE Aviation

- Fred Fisher, AVSI

- John Gerard, Smiths Aerospace

- Dorina Hester, Boeing

- Gary Horan, FAA

- Yoonjin Kim, Texas A&M University

- Tod Lanham, GE Aviation

- John Lapointe, FAA

- Aaron Larson, Honeywell

- John Lewis, FAA

- Barbara Lingberg, FAA

- David Lund, AVSI

- Emmanuel Papadopoulos, FAA

- Eric Peterson, Honeywell

- James Peterson, Honeywell

- David Redman, AVSI

- Leanna Rierson, Digital Safety Consulting

- Tom Sherman, GE Aviation

- Tim Theriault, GE Aviation

- Craig Treece, Lockheed Martin

- Kurt Woodham, NASA

The authors would also like to thank all other technical experts and document reviewers who supported the AVSI AFE43 project.

# TABLE OF CONTENTS

|      |                                                          |                                                        |                                                         | Page |

|------|----------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------|

| EXEC | CUTIVI                                                   | E SUMN                                                 | MARY                                                    | ix   |

| 1.   | INTRODUCTION                                             |                                                        |                                                         | 1    |

|      | 1.1                                                      | Scope                                                  |                                                         | 2 3  |

|      | 1.2                                                      | Docur                                                  | ment Organization                                       | 3    |

| 2.   |                                                          |                                                        | RY CONSIDERATIONS FOR MICROPROCESSOR-BASED APPLICATIONS | 4    |

| 3.   | THE COTS MICROPROCESSOR COMMON RISKS AND RISK MITIGATION |                                                        |                                                         | 6    |

|      | 3.1                                                      | Visibi                                                 | ility and Debug                                         | 7    |

|      |                                                          | 3.1.1                                                  | Target Computer Environment                             | 7    |

|      |                                                          | 3.1.2                                                  | Simulated Computer Environment                          | 9    |

|      | 3.2                                                      | Confi                                                  | guration-Related Issues                                 | 10   |

|      | 3.3                                                      | Resou                                                  | arce-Sharing Considerations                             | 12   |

| 4.   | SAFETY NETS                                              |                                                        | 13                                                      |      |

|      | 4.1                                                      | Microprocessor Selection and Safety Net Considerations |                                                         | 15   |

|      |                                                          | 4.1.1                                                  | First-Time Use                                          | 15   |

|      |                                                          | 4.1.2                                                  | Availability                                            | 15   |

|      |                                                          | 4.1.3                                                  | Stability                                               | 16   |

|      |                                                          | 4.1.4                                                  | Suitability                                             | 16   |

|      |                                                          | 4.1.5                                                  | Testability                                             | 17   |

|      | 4.2                                                      | 2 Safety Net Monitor Considerations                    |                                                         | 17   |

|      |                                                          | 4.2.1                                                  | Hardware Monitor Considerations                         | 17   |

|      |                                                          | 4.2.2                                                  | Software Monitor Considerations                         | 18   |

|      |                                                          | 4.2.3                                                  | External Monitor Considerations                         | 18   |

|      |                                                          | 4.2.4                                                  | Internal Monitor Considerations                         | 19   |

|      | 4.3                                                      | Archit                                                 | tectural Safety Net Examples                            | 19   |

|      |                                                          | 4.3.1                                                  | Shared Resource Approach                                | 19   |

|      |                                                          | 4.3.2                                                  | Lock-Step Approach                                      | 21   |

|      |                         | 4.3.3 Frame-Lock Approach                                            | 21       |

|------|-------------------------|----------------------------------------------------------------------|----------|

|      |                         | 4.3.4 Dissimilar Architectures                                       | 22       |

|      |                         | 4.3.5 Aircraft-Level Safety Assurance                                | 22       |

|      | 4.4                     | Safety Net Conclusion                                                | 22       |

| 5.   | RESULTS AND FUTURE WORK |                                                                      | 22       |

|      | 5.1<br>5.2              | Results<br>Future Work                                               | 22<br>23 |

| 6.   | REFE                    | FERENCES                                                             |          |

| 7.   | GLOSSARY                |                                                                      |          |

| APPE | ENDICE                  | ES                                                                   |          |

|      |                         | Research Experiments Configuration-Related Issues Backup Information |          |

# LIST OF FIGURES

| Figu | are                                       | Page |  |

|------|-------------------------------------------|------|--|

| 1    | Scope of the Handbook                     | 3    |  |

| 2    | Freescale MPC8572 Device Disable Register | 10   |  |

| 3    | Freescale MPC8572 Block Diagram           | 12   |  |

#### LIST OF ACRONYMS

AEH Airborne electronic hardware

AVSI Aerospace Vehicle Systems Institute

BIST Built-in self test

BIT Built-in test

CCB Core Complex Bus

CCSRBAR Configuration control and status base address register

COTS Commercial off-the shelf CRI Certification review items

DEC Decrementer

DoS Denial of service

EMI Electromagnetic interference FAA Federal Aviation Administration FPGA Field-programmable gate arrays

I/O Input/output

IDE Integrated development environments

IP Intellectual Property

L2 Level 2

MMU Memory management unit

OS Operating system

PCI Peripheral component interconnect-express

RAM Random access memory SEU Single event upset

SoC System-on-a-chip

UART Universal asynchronous receiver/transmitter

WCET Worst-case execution time

WDM Watchdog monitor

#### **EXECUTIVE SUMMARY**

This Handbook provides research information intended to help aerospace system developers and integrators and regulatory agency personnel in the selection and evaluation of commercial off-the-shelf (COTS) microprocessors for use in aircraft systems. Airborne electronic hardware (AEH) includes modern state-of-the-art and highly integrated COTS microprocessors that (1) may not provide adequate visibility and debug features to reveal internal functionality, (2) are less predictable due to the interaction of advanced features, (3) have programmable configuration capabilities available to application software, and (4) share resources across multiple cores and devices. These highly complex COTS microprocessors are becoming more challenging to test and to determine that they satisfy applicable functional and safety-related requirements.

Resolutions to certification process challenges should offer the possibility of establishing and maintaining standards that support the continual change and growth of technologies and operations. Such resolutions can include

- establishing qualitative as well as quantitative methods to certify aircraft with embedded nondeterminate complex or critical applications.

- establishing accepted standards of architectural patterns for critical, complex systems and methods for validation and design assurance.

- establishing industrywide accepted methods for design assurance of COTS microprocessor and microprocessor-based systems.

- streamlining the certification process.

This Handbook is based on the cooperative research accomplished by contributing members of the aerospace industry and the Federal Aviation Administration (FAA) as part of the Aerospace Vehicle Systems Institute Microprocessor Evaluations Projects 1 through 5. The research underlying this Handbook addressed the use of COTS microprocessors and systems-on-a-chip (SoC) in safety-critical avionics. The project objectives were to (1) identify common risks of using SoCs and mitigation techniques to provide evidence that they satisfy regulatory requirements and (2) evaluate existing regulatory policy and guidelines against the emerging characteristics of complex, nondeterministic microprocessors, and SoCs to support the certification of aircraft and qualification of systems using these devices.

Considering the growing complexity of microprocessors, the research revealed the increasing impracticality of providing safety assurance at the device level alone. The combination of growing complexity of both software and hardware will drive the need to evaluate large complex systems at the system level. The rate of change and growing complexity is accelerating, and the time between new generations of hardware and software is shrinking. The complexity of most COTS components has grown and continues to grow beyond the capability to exhaustively test them. The overlapping phases of development, certification, deployment, and life cycle maintenance together with COTS obsolescence accentuate the need for rapid and evolving

methodologies. FAA policy, guidelines, and practices may need to be updated to accept these methodologies.

Complex aircraft system development requires more robust consideration of system failure and anomaly detection, correction, and recovery. The safety net approach identified in this Handbook also may provide a means to reduce the growing difficulties and costs of design assurance for highly integrated, complex, nondeterministic AEH and software within aircraft systems, and to reduce the labor burden for FAA regulation compliance and design assurance.

A safety net is defined herein as the employment of mitigations and protections at the appropriate level of aircraft and system design to help ensure continuous safe flight and landing. The safety net methodology focuses on the assumption that a microprocessor will misbehave. The ability to protect against unexpected behavior, damage, injury, and instability over the service life outside, or at a level above the device itself, is necessary as appropriate for the design assurance level.

The safety net approach is an alternative way to mitigate the risks associated with COTS microprocessors via both passive and active methods designed into aircraft systems. If it is not feasible to show that complex aircraft systems are sufficiently free of anomalous behavior by evaluating system components, the safety net alternative can mitigate unforeseen or undesirable COTS microprocessor operation by detecting and recovering from anomalous behavior at the operational system level. This approach requires the safety net to be designed as a function within the aircraft system. The safety net can include passive monitoring functions, active fault avoidance functions, and control functions for recovery of system operations. System architecture and control and recovery functions should be designed to facilitate effective system recovery from anomalous events. Safety nets should show that systems are sufficiently impervious to anomalous behavior by ensuring continuous functional availability and reliability, satisfying applicable regulations, and meeting airworthiness requirements. This includes verifying any disabled functionality from the COTS will remain inactive in the specific application.

A multilevel safety net approach is required for complex and critical applications in systems that cannot be fully assured at the component level and is significantly linked to the assigned design assurance level required by regulation, contractual obligation, and the integrated complexity at the device level. The design of safety nets, in general, is becoming a complex, application-specific art form that will be required to detect, resolve, and validate recovery in a run-time environment to the required levels of availability and safety. The safety net approach documented in this Handbook is consistent with current FAA policy and guidelines.

The use of COTS microprocessors may be predominant in future aerospace systems. The use of COTS microprocessors avoids the drastically increasing costs of custom microprocessor design. This Handbook does not address the use of custom device design.

#### 1. INTRODUCTION.

This Handbook is based on Aerospace Vehicle Systems Institute (AVSI) Microprocessor Evaluations Projects 1 through 5 [1-5]. Microprocessors and systems-on-a-chip (SoC) have become extremely complex and densely packaged. Recent changes in commercial off-the-shelf (COTS) microprocessors can be characterized as both physical and functional changes. Physically, transistor density has continued its exponential increase, allowing for hundreds of millions to billions of transistors to be placed on a single device. As of 2010, 65- and 45-nm devices are common in the COTS marketplace, and 32 nm and smaller devices are beginning to enter the marketplace or are on the near horizon. In addition to decreased device size, the functional capability of COTS devices has expanded. It is no longer necessary for different system components to be implemented as discrete devices. Instead, a single COTS SoC may contain multiple microprocessor cores, input/output (I/O) devices, memory controllers, and other functionality. As a result, deterministic performance is difficult or impossible to predict in some cases. These devices require additional evaluation methods beyond that identified in current regulatory requirements to achieve the resilience required to meet safety and reliability requirements. Aircraft systems that contain these COTS devices may require multilevel safety nets to be designed into them.

This Handbook has been written for experienced system designers and regulatory personnel. It is intentionally not prescriptive in nature. It is intended to support the development of new approaches to the design assurance and safety evaluation leading to the approval of airborne systems. The design of an airborne system, the selection of airborne electronic hardware (AEH) (e.g., microprocessor) devices within the system, and the architecture of the system will be unique for each application. The potential sources of nondeterminism and the challenges of design assurance of AEH devices must be determined for each system. This Handbook does not attempt to identify sources of microprocessor nondeterminism because they will be unique for each system and will proliferate in the future. System designers have to evaluate the risks associated with the candidate microprocessors and design the system architecture and the safety nets to mitigate these risks.

This Handbook does not constitute Federal Aviation Administration (FAA) policy or guidance; rather, it is the result of FAA- and industry-funded research and may contribute to future policy or guidance.

The purpose of this Handbook is to

- document common areas of concerns regarding the use of COTS microprocessors in complex and/or safety-critical systems.

- provide approaches, information, and examples for mitigating the concerns through a safety net.

- provide access to the research on which the content of this Handbook is based.

- provide example approaches to resilient systems through methods defined in this Handbook under the overarching term safety nets.

- reveal how existing regulatory policy and guidance may be augmented to support the creation of resilient systems through safety net approaches safeguarding the use of microprocessor technologies in complex and/or safety-critical systems.

# 1.1 SCOPE.

This Handbook can be used for the development and approval of aerospace systems containing embedded COTS microprocessors.

Note: Within this Handbook the term "microprocessors" shall be understood to include COTS microprocessors and SoCs unless otherwise specified. The term SoCs will be used when the text refers to only SoCs. The overloaded term microprocessor may tend to camouflage the differences between the two; therefore, it is highly recommended that users planning to use SoCs in aircraft systems fully understand the technical differences between microprocessors and SoCs.

The intended users include system developers, integrators, and all personnel in both industry and the FAA responsible for aircraft certification and system qualification.

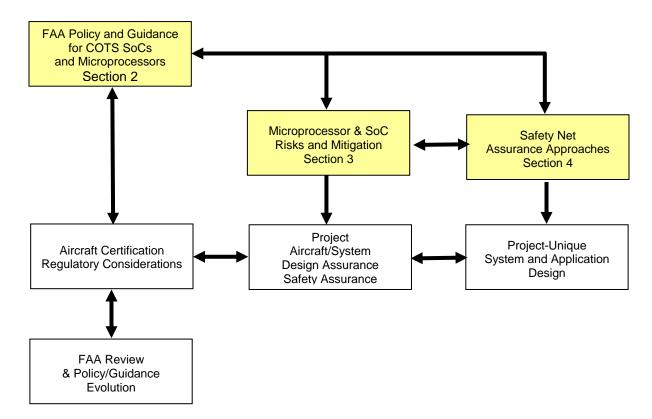

As shown in figure 1, the Handbook relates current FAA policy and guidance (section 2) to both microprocessor and SoC risks and risk mitigation (section 3) and safety net assurance approaches (section 4). As described in section 3, the device risks and risk mitigation considerations may be used by project personnel to consider in the use of COTS microprocessors in aircraft systems. The safety net assurance approaches may be considered by project personnel as an approach to mitigating these risks. The information in this Handbook is intended to provide system design and safety assurance approaches that facilitate the use of complex COTS microprocessors without incurring the difficulties associated with legacy methods of design assurance by test and analysis of components. This Handbook is also intended to aid FAA personnel during aircraft certification and policy review. The authors hope the use of COTS microprocessors and their associated safety net approaches in aircraft systems will lead to enhanced FAA policy and guidance over time.

Both the FAA and aerospace industry members participated in the research on which this Handbook is based. Use of the Handbook content should be coordinated between project and regulatory personnel.

Acceptance of the safety net and the related assurance approaches documented in this Handbook are predicated upon the mutual development and acceptance of the project-unique design and assurance methodologies and their effectiveness in meeting safety and airworthiness requirements.

Note: The yellow blocks identify the scope of the Handbook.

Figure 1. Scope of the Handbook

#### 1.2 DOCUMENT ORGANIZATION.

- Section 1 identifies the purpose and scope of this Handbook and identifies the research on which it is based.

- Section 2 provides an overview of the current regulatory considerations for using COTS microprocessors in airborne systems.

- Section 3 provides an overview for using COTS microprocessors, and some of the risks of using microprocessor technologies are described. These risks are described in terms of hardware and software considerations; tool use and limitations; development environments, information requirements and constraints, performance monitoring, fault insertion and analysis; simulation uses and constraints; and programmable characteristics (e.g., configuration control, excessive capabilities and disabling/enabling features, emerging technologies, and the resource-sharing effect on timing).

- Section 4 introduces safety net approaches; related changes to design, development, and safety; integrated device characteristics; operational considerations of safety nets, error/anomaly detection, recovery, and validation mechanisms; and architectural requirements for safety nets.

- Section 5 summarizes the Handbook and the future research that can be based on its content.

- Section 6 provides references.

- Section 7 contains a glossary defining the terminology used in this Handbook.

# 2. REGULATORY CONSIDERATIONS FOR MICROPROCESSOR-BASED AIRBORNE APPLICATIONS.

Current FAA policy and guidance does not directly address the use of COTS microprocessors and SoCs in aircraft systems. However, the existing policy and guidance can be used as a basis from which this Handbook builds upon to help provide an applicant with an acceptable means of demonstrating that their system meets the applicable airworthiness requirements.

FAA Advisory Circular AC 20-152 [6] notes that hardware life cycle data may not be available to satisfy the objectives of RTCA/DO-254, and therefore, alternative methods or processes are required to ensure that COTS microprocessors perform their intended functions and meet airworthiness requirements. No other guidance regarding COTS microprocessors is provided.

FAA Order 8110.105 [7] limits the discussion of COTS components to COTS Intellectual Property (IP), which it defines as commercially available, functional logic blocks that are implemented within custom micro-coded components, such as programmable logic devices, field-programmable gate arrays (FPGA), or similar programmable components. Although no specific policy or guidance is provided for COTS microprocessors, it does mention COTS processor cores. Many of the concerns presented in FAA Order 8110.105, section 4-9.b also apply to COTS microprocessors:

- "(1) COTS components, including IP, are developed by a company other than the applicant and hardware developer. Intended to provide specific functions or abilities in many different applications, COTS components may or may not have been developed using a rigorous design assurance method (such as RTCA/DO-254). Given this, we must ensure that the applicant and hardware developer show that using COTS IP complies with the applicable airworthiness requirements, regulations, policy and guidance for that project." [7]

- "(2) Availability of COTS IP doesn't automatically guarantee that it can be used in a manner that complies with airworthiness requirements, regulations, policy and guidance. Depending on the complexity of the COTS IP and the availability of IP documentation, applicants and/or hardware developers may have significant work to show compliance for the system or equipment." [7]

- "(3) Using a COTS IP in a simple electronic hardware/complex electronic hardware (SEH/CEH) device that is installed in airborne systems or equipment should satisfy applicable functional and safety-related requirements. RTCA/DO-254 Section 11.2 may not be sufficient for design assurance of a

COTS IP implemented in a SEH/CEH that supports level A and B aircraft, and other safety critical, functions. As a result, applicants may need to develop or augment system architectural mitigation, component verification, testing, analysis and other life cycle data of a COTS IP. All this is needed to demonstrate its intended function, show it is free from anomalous behavior, satisfies applicable regulations, and meets airworthiness requirements." [7]

Although FAA Order 8110.105 does not specifically address COTS microprocessors, many of the issues applicable to COTS IP also apply to COTS microprocessors and SoCs, and therefore, some of the guidance of section 4-9.b.(4) of the Order can be used as a basis for the techniques presented in sections 3 and 4 of this Handbook:

- Paragraph (b) states that the applicant and system developer can use extensive testing and analysis to gain detailed information about the functionality, and how it operates during boundary and failure conditions. This should include testing and analysis of any functionality that will not be used or activated in the specific application. Section 3 of this Handbook presents some examples of activities that the system developer can perform to gain a better understanding of the system and, therefore, design mitigation techniques to avoid or contain an undesirable or catastrophic action by the microprocessor.

- Paragraph (c) states that architectural mitigations at the device, board, line replaceable unit, or system level can be employed to detect and/or mitigate unforeseen or undesirable operation. Sections 3 and 4 of this Handbook present some examples of mitigation techniques that the system developer can employ to eliminate or minimize the effect of an error that occurs as a result of an event either internal or external to the microprocessor.

Note that it is not intended for the techniques in this Handbook to be applied to COTS IP soft processor cores, since it is expected that the developer will have the appropriate life cycle data available and DO-254 processes apply [8].

The techniques presented in this Handbook are intended to help developers provide additional layers of protection through the development of mitigations that are incorporated at the appropriate level of the design. As microprocessor technologies continue to evolve, these techniques will become more critical in assuring the safe operation of the airborne systems in which they are employed. However, it is important to note that these techniques, such as safety nets, are in addition to, and do not replace, current FAA-accepted methods for selecting a microprocessor and designing and testing the system in which it is used. These methods include:

- Testing operating system and hosted applications on the actual hardware to be approved.

- Monitoring current errata sheets and technical notes so that developers are aware of known or newly discovered problems, undocumented features, and microprocessor limitations that may adversely affect system operation. There should be a process in

place to determine if any actions are required as a result of changes to the errata sheets or technical notes.

- Establishing and maintaining a configuration control plan for the microprocessor throughout the life cycle of the system. There should be a process established for the microprocessor manufacturer to provide notification of any changes to the microprocessor, and for the design approval holder to review the changes and determine the effect on the operation of their system.

- Microprocessors used in applications where failure could result in catastrophic or hazardous failure conditions should have appropriate service experience so that the applicant has confidence that the device is mature and design deficiencies are known.

- The microprocessor should be operated within the environmental limits established by the microprocessor manufacturer. If these limits are exceeded in the operational environment, the applicant should verify through testing that all production microprocessors will meet the system environmental requirements.

As previously noted, the airborne market for these devices is insignificant when compared to other markets such as consumer electronics, automobiles, and telecommunications. Applications in these other markets are less susceptible to anomalous behavior resulting from internal and external events. Therefore, the aviation industry should learn how to cope with the increasing complexity and resulting vulnerabilities of these devices. The authors of this Handbook hope that the techniques and guidance provided herein will be used by system developers to better understand and mitigate the vulnerabilities of their devices, and that certification authorities will embrace these techniques and continue to pursue relevant policy and guidance to the aviation community.

#### 3. THE COTS MICROPROCESSOR COMMON RISKS AND RISK MITIGATION.

This section provides an overview of using COTS microprocessors and the risks presented by their deployment in aerospace systems.

It is important to distinguish between discrete COTS microprocessors and SoCs when discussing certain elements of risk and safety analysis. The task of ascertaining safety considerations is more complicated for SoCs due to the broad variety in SoC designs. Unlike the case of discrete COTS microprocessors, where the majority of features of interest are similar across most microprocessors, SoC components tend to vary significantly based on the product selected, making safety analysis more complicated. Not only are the safety concerns due to the features of individual IP cores an issue, but interaction amongst them presents a verification challenge to system designers. Additionally, certain systems using SoCs may not require particular on-chip cores and would require the disabling of those cores for safety reasons.

Resources used by safety nets are expected to change as the underlying technology of the system it is protecting (or implemented within the safety net itself) evolves. An example of this occurs when configuration register changes (the addition of new, removal of old, exposure of

hidden/reserved registers) are needed because separate, discrete microprocessors; system controllers; and other components are replaced with a single SoC. The safety net design must be examined and perhaps adjusted when such technology changes are implemented or when the device must be approved within a new application. The discussion above needs to be considered while formulating a safety net.

After reviewing the designs of a variety of modern COTS microprocessors across a group of manufacturers, product families, and technology generations, three areas of common risk were identified for all these devices [4]:

- Visibility and Debug—the inability to observe the internal operation of the device during system use and development (see section 3.1.).

- Configuration-Related Issues—software accessibility to device configuration during system operation (see section 3.2).

- Resource-Sharing Considerations—performance unpredictability due to multiple on-chip shared resources (see section 3.3).

#### 3.1 VISIBILITY AND DEBUG.

During background research, a physical target computer environment and a simulated target computer environment were setup to perform experiments. Setting up these environments exposed visibility and debug challenges that could arise during system development and analysis; some of these challenges are described in the remainder of this section. The system developer should document the configuration of the test environment and identify any differences, limitations, and constraints of the simulated environment, if used, in relation to the physical environment. Based on the visibility and debug challenges identified, system developers should consider the following items when setting up their evaluation environment.

#### 3.1.1 Target Computer Environment.

A target, or physical, computer environment was established to perform experiments and provide evidence and insight, which led to the conclusions of the research. The target computer environment included a development board for the SoC selected for evaluation, board support software, a COTS operating system, and COTS tools for development and debug. (Details can be found in reference 5.) The following software and hardware considerations were noted during the target computer environment evaluation.

#### Software considerations:

Software integration—Operating systems, license agreements, and board support software are typically included with target development boards. System developers should work closely with the integrated circuit device manufacturer when setting up the development environment to ensure compatibility of tools selected for the development environment.

- Debug capabilities—Tools provide visibility and debug capabilities to assist with system and application software development. These tools should be evaluated to verify that they provide the capabilities needed for the system being developed.

- Multicore support—Additional tool capabilities are required to effectively use, debug, and develop multicore SoC applications. Beyond the typical compile and debug capabilities used in single-core development, individual and group control of the processing cores are important in testing multicore applications. Also, some projects may require programming language support for multicore development, including multithreading capabilities and shared access to on-chip devices.

- Integrated development environments (IDE) for safety-critical embedded systems— Safety-critical embedded system designers may find that they are limited in the available choices for IDE compared to standard embedded system development. Applicants should be aware of the IDE's suitability with respect to their specific project requirements in addition to tool qualification issues.

#### Hardware considerations:

- Limited visibility into device internal operation—manufacturer documentation is intended to support the use of the device based on the capabilities described in the User's Manual and device characteristics documented in the data or errata sheet. The internal operation is frequently proprietary information. For example, the User's Manual may document how to configure the use of cache memory, but the cache algorithm being used internally by the device may be proprietary.

- Performance monitoring—Hardware performance monitors may be provided by the manufacturer to provide insight into the internal operation of a microprocessor. These monitors allow system designers to track various system activities and performance statistics during application development and execution. Typical uses of hardware performance monitors include gathering level 1 and level 2 cache statistics and measuring cycle counts to estimate application execution times. Performance monitors may also allow a system designer to observe the activity of functions resident on the microprocessor, including memory controllers, PCI-Express (PCIe) and Ethernet controllers, and direct memory access engines. These performance monitors are uniquely designed for each COTS microprocessor, and access to the performance monitors typically requires custom software and is not fully supported by COTS operating systems.

- Fault insertion—The ability to insert faults internal to the microprocessor may be limited or not achievable. An applicant may not be able to demonstrate that faults are correctly detected if the faults cannot be injected. The safety net methodology should mitigate these types of faults.

• Industry benchmarks—The use of industry benchmarks may help demonstrate timing characteristics and the potential effect of shared resources on timing. The benchmarks that were investigated used memory to simulate the hardware I/O and did not exercise the microprocessor-shared hardware resources on the target computer. The limitations of industry benchmarks to fully exercise microprocessor behavior should be understood and augmented with other tests.

# 3.1.2 Simulated Computer Environment.

A simulated computer environment was established to perform experiments and provide evidence and insight, which led to the conclusions of the research. The environment included a host environment, a simulation of the microprocessor device selected for evaluation, COTS simulation support software, a COTS operating system, and COTS tools for development and debug. The following software and hardware considerations were noted during the simulated computer environment evaluation.

#### The software considerations were:

- Applicants should be aware that the primary focus of the microprocessor simulation is on application software development. Typically, hardware evaluation is a secondary concern, if addressed at all.

- Modeling configuration and internal registers—The simulated computer environment typically models the minimum set of configuration and internal registers to support software execution. The differences between the simulated computer environment and the target computer should be documented by the system developer as part of the test environment. Evaluating the system response in a simulated environment requires accurate modeling of all configuration registers.

#### The hardware considerations were:

- Limited modeling of hardware—Hardware interfaces and modeling of microprocessor functions may be limited to those items required for application software development.

- The timing and cycle accuracy of the simulated target computer should be assessed. If the target computer model is not cycle accurate, functions which are timing sensitive should be verified in the target computer environment.

- Modeling of device performance—Internal microprocessor performance monitors may not be modeled in the simulator.

- Focus of microprocessor models is on the simulation of core central processing units, modeling of other microprocessor-resident functionality may be limited.

#### 3.2 CONFIGURATION-RELATED ISSUES.

Configuration register changes are a growing concern for avionic microprocessor applications since continued device integration has allowed an increasing proportion of the entire system to be configured through software. If a microprocessor is not configured properly, erroneous behavior, including improper data processing, stack overflows, erroneous interrupts, machine checks, data loss, data corruption, or inadequate throughput, may occur.

Over time, the number of configuration registers per microprocessor has grown significantly. For example, the Freescale<sup>TM</sup> MPC8572 SoC has more than 500 software-accessible configuration registers that control basic functionality of the processing cores and on-chip devices [9]. In addition to these configuration registers, various device functions may be set externally via pullup/pulldown pins, which are sampled shortly after a hardware reset or internally via software. Incorrect settings or inadvertent changes are areas of concern that must be addressed.

In general, the capabilities of most microprocessors exceed what is required by typical applications. Care should be taken to provide assurance that unused capabilities are properly disabled. In legacy avionics with many discrete system devices, this concern was addressed through physical disconnection of the unused devices to power sources and the rest of the system. However, COTS SoCs have removed the physical separation between devices and processors and have given control of device configuration to software. Therefore, the deactivation of unused features has become an additional consideration within the set of configuration-related issues. In addition to proper deactivation of unused features and devices, system designers should assure that those features and devices cannot be reactivated through erroneous software or environmental effects. Inadvertent activation of an unused device may cause unintended and undesirable operation, such as erroneous interrupts, data loss, data corruption, machine check cycles, and stack overflow, among others.

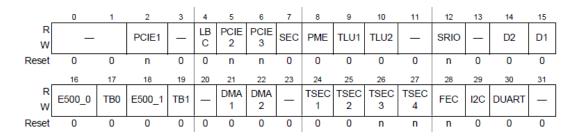

As an example of how the deactivation of unused features has changed for modern COTS microprocessors, figure 2 shows the Freescale MPC8572 device disable register.

Figure 2. Freescale MPC8572 Device Disable Register [9]

This register is used by the system to determine whether each of the major on-chip devices of the system should be enabled or disabled by setting particular fields of the register to 0 (enabled) or 1 (disabled). This configuration register contains 24 single-bit readable and writeable fields that are associated with the 24 on-chip devices of the SoC. For example, bits 16 and 18 control the

two E500 processing cores [10], bits 2, 5, and 6 control the three PCIe controllers, and bits 24 through 27 control the four triple-speed Ethernet controllers. A single bit flip in this register can disable a critical on-chip device or one of the processors, and research has demonstrated that erroneous writes to this register can render the system inoperable [5]. Therefore, system designers should be aware of the risks of software erroneously modifying the system configuration space.

Several microprocessor devices also offer the user the flexibility of locating the configuration registers in external memory space, which makes them more vulnerable to corruption. This capability also makes the system susceptible to loss of all configuration data if the pointers to the external memory locations are corrupted.

Configuration registers may change by software errors (inadvertent writes), by single event upsets (SEU), hardware defects, hardware faults (such as a noisy power supply core voltage, signal integrity issues, ground bounce, etc.), or electromagnetic interference (EMI). Refer to appendix B for a description of power supply-related issues.

In light of the risks identified with the current technology and trends and the criticality of proper microprocessor configuration register settings, the risks associated with incorrect configuration register settings should be understood. Each register should be assessed for:

- Intended setting for each register bit within the system being implemented and the reason for selected setting

- Identification of each operational phase at which each register is being set (i.e., initial power up, power on reset, built-in test (BIT), and exception processing)

- Identification of disabled functions

- Impact to system if the state of the register bit is unintentionally changed

- It is recommended that the impact of an inadvertent change to critical registers or registers of questionable impact, be verified through simulation, if possible.

- The simulation environment should implement an algorithm that has the ability to randomly change configuration settings.

- Timing and rate of impact to system of an unintentionally changed register bit.

- Errata sheet information

Once this analysis has been completed, safety net methodologies can be employed to mitigate the identified risks. Refer to section 4 for information on safety net methodologies.

#### 3.3 RESOURCE-SHARING CONSIDERATIONS.

Modern microprocessors differ from previous technology in that many processing, memory, and I/O components reside within a single device, and many of these components are designed to be shared to optimize system performance. The multiple processing components compete to initiate requests to their memory and I/O targets. Additionally, the I/O components can initiate requests to memory targets through direct memory access. Whether initiated by a processor or I/O controller, requests travel over shared on-chip interconnects, typically a single on-chip bus. This Handbook defines shared resources as any on-chip or off-chip components that are accessible to multiple initiators. Examples of shared resources include on-chip memory controllers, hardware accelerators, level 2 (L2) and/or level 3 caches, on-chip busses and, on-chip Ethernet controllers.

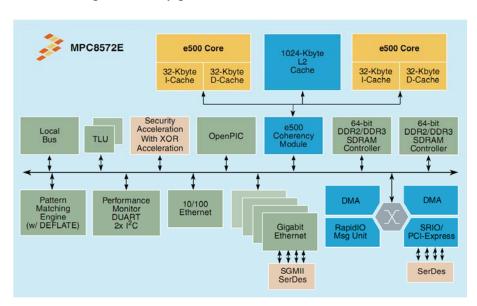

Modern microprocessors feature a number of shared resources. As shown in figure 3, the two e500 cores of the Freescale MPC8572 share a single L2 cache [9]. Additionally, the two processing cores share a single on-chip bus to access the other major components of the system, including the various I/O controllers and memory controllers.

It is highly recommended that the system designer analyze the access protocol for these shared resources and the run-time behavior of all programs that share a given resource. Based on this analysis, the designer should ensure that even with the sharing of resources, the system will continue to run in a predictable manner (continuous operation). In some conditions, hard shutdowns can be an acceptable safety protection mechanism.

Figure 3. Freescale MPC8572 Block Diagram [9]

Sharing resources is a major contributor towards nondeterminism and worst-case execution time (WCET) analysis challenges in modern COTS microprocessors. Nondeterminism arises because the availability of a shared resource becomes largely dependent on the run-time behavior of other processes sharing the same resource. In many cases, the run-time behavior of programs is data-dependent and cannot be predicted offline. WCET analysis depends on understanding all

conditions that lead to timing delays and then bounding for worst-case conditions. Multiple shared resources on a single device complicate this analysis due to the great increase in the number of delay conditions.

Pellizoni, et al. [11], describe the challenges in predicting the WCET in a multitasking system. They show that, due to the interference between cache-fetching activities and I/O peripheral transactions, tasks can suffer computation time variance of up to 46% in a typical embedded system.

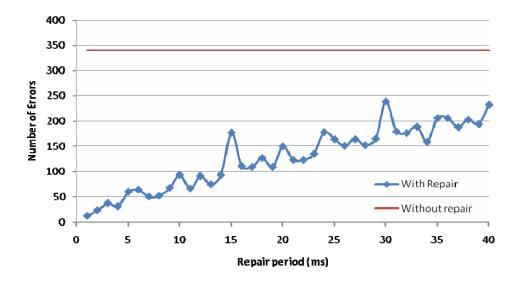

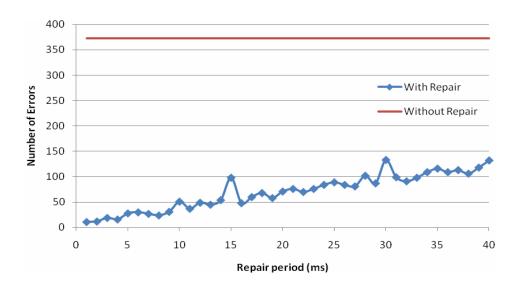

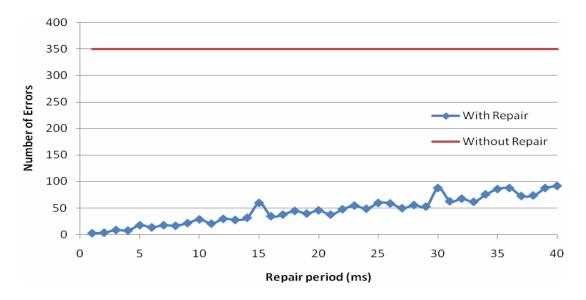

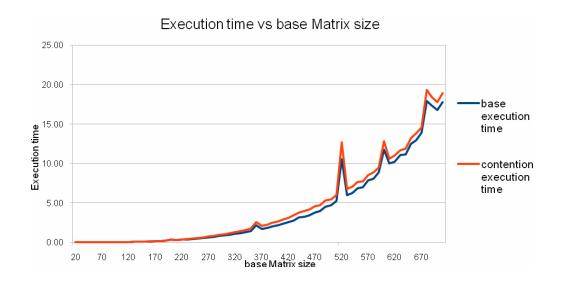

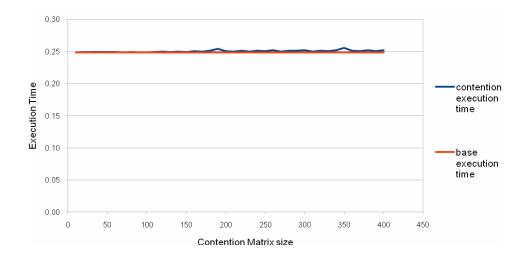

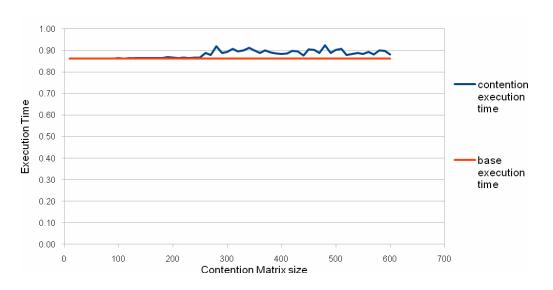

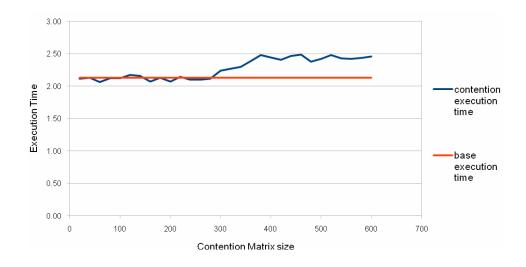

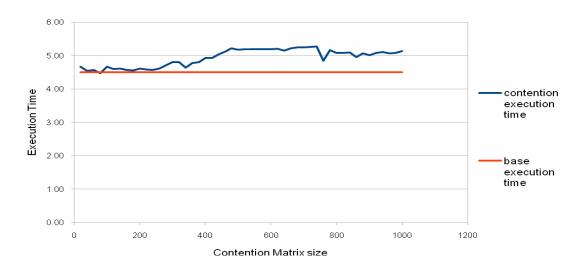

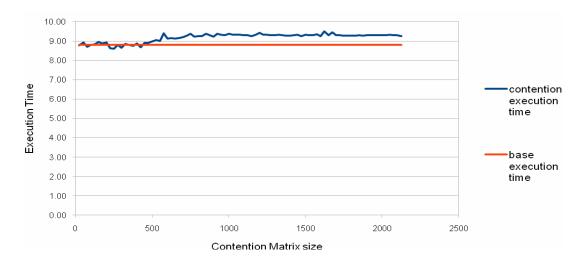

To further assess the timing delays and nondeterminism caused by resource sharing, additional experiments were performed using a simple matrix multiplication program on the Freescale MPC8572 platform considering the L2 cache as the shared resource [5]. Each processing core executed its own copy of a matrix multiplication program that required using the shared L2 cache due to the program size. The experiments showed that the execution time of the matrix multiplication program can increase by as much as 17% as L2 cache interference increases.

Moscibroda, et al. [12], describe that in a multicore system, multiple programs running on different cores can interfere with each other's memory access requests, thereby adversely affecting performance. They show that a competing program running on one processing core can result in a denial of service (DoS) on the other processing core, due to the inherent unfairness in memory controller access policy. The performance of a blocked application can be reduced by as much as 2.9 times in a typical dual-core system. Moscibroda, et al., identify the memory access scheduling algorithm as the main source of inequality in memory access, allowing the DoS to occur. Shared resource access policy and scheduling is addressed in section 4.3.1.

Industry trends indicate that the ratio of processing cores to various shared resources in COTS SoCs will increase over time. Instead of two processing cores sharing a common cache, memory controllers, and I/O devices, there will be four, eight, or more processing cores sharing these resources. This will increase the competition for shared resources among processing cores, worsening potential unpredictability issues.

#### 4. SAFETY NETS.

A safety net in the context of this Handbook is defined as the employment of mitigations and protections at the appropriate level of aircraft and system design to help ensure continuous safe flight and landing.

Assuring that the microprocessor is absent of uncertainty at the device level alone is no longer feasible; therefore, a multilevel safety net becomes essential. A multilevel safety net concept considers the discrete devices, the circuits, individual components directly supporting the use of microprocessors, and higher-level system architectures. The multilevel safety net can be viewed as an architectural approach.

Multilevel safety net protection is significantly linked to the assigned design assurance level required by regulation and/or contractual obligation and the integrated complexity at the device

level. Modern microprocessor technology necessitates the need for a multilevel safety net. For example, failure of a flight control system may result in a catastrophic condition, whereas the failure effects of a lavatory system may be limited to passenger discomfort. Therefore, a safety-critical system using a particular microprocessor requires a higher level of safety than a nonessential system using the same microprocessor. This demonstrates the need for a multilevel safety net approach where the safety net may respond differently in different levels of criticality. A failure in the flight control system will most likely require a high-priority response with limited recovery time, while a failure in the lavatory may only require a low-priority response with a longer recovery time. Error detection and recovery from anomalous conditions may occur at different hierarchical levels within the system (e.g., chip level, board level, subsystem, or system).

Since the criticality of the lavatory system is lower than the flight control system, fundamentals for a multilevel safety net should be established as an acceptable approach.

Industry research has shown that the susceptibility of random access memory (RAM)-based devices to external stimuli, such as cosmic rays (resulting in single event effects), lightning, and EMI, is generally greater than the devices that employ flash-based technology [13]. However, disregarding the potential effects of these types of threats on flash-based memory could lead to the same risks as the threats on RAM-based memory. For example, a multilevel safety net implementation in RAM-based designs that incorporate periodic memory content verification (scrubbing) to help ensure error-free operation in a flight-critical system may also incorporate the use of a non-RAM-based monitoring circuit and/or the use of an external discrete monitoring circuit. Since the safety net implementation would require the ability of both the primary and monitoring circuits to work together to provide the overall integrity, the monitoring circuit should be less susceptible to external threats as the primary circuit. A safety net implementation using the same device in a low-criticality system, such as the lavatory example, may use only a high-level monitor component, since system response time is of little concern.

Another example that continues to challenge the use of modern, highly integrated, complex devices are the core voltage (rail voltage) of COTS microprocessors. As the core voltages continue to decrease, it becomes more difficult to ensure that the devices are not susceptible to supply voltage fluctuations, noise, and environmental effects. Current industry data show that, as the size of the device decreases, the margin between the applied voltage and the parasitic energy of the device leads to unpredictable and unstable conditions.

The safety net methodology assumes that a microprocessor will misbehave. The absence of a properly implemented safety net reduces the ability to protect a system against the unexpected behavior, damage, injury, or instability of a device during its service life. Architectural designs, in general, are becoming a more complex, application-specific art form requiring the ability to detect, resolve, and validate component failure in a run-time environment to the required levels of availability and safety. The safety net methodology does not ensure determinism solely at the device level. Rather, safety nets are intended to provide the ability to protect against unintended or misleading behavior using a multilevel approach.

# 4.1 MICROPROCESSOR SELECTION AND SAFETY NET CONSIDERATIONS.

DO-254 does provide some guidance (see section 2) for the use of COTS products [8]. Further guidance and clarifications to DO-254 are provided in FAA Order 8110.105 Change 1 [7]. The safety net and system architecture should be designed concurrently, employing one or more of the techniques previously discussed as well as taking into consideration first-time use, availability, suitability, stability, and testability traits of the microprocessor.

Device selection continues to be a regulatory concern as microprocessor technology advances. This section was developed in part from research, from DO-178B [14] and DO-254 [8], and largely from existing issue papers and certification review items (CRI) that have been levied on a project-by-project basis by the regulatory agencies. The specific CRI and issue papers are considered to be confidential to the project for which they are levied against; therefore, the information contained within this Handbook is presented from a generalized viewpoint.

It has been expressed by the regulatory authorities through CRI and issue papers and DO-254 that in using a microprocessor, the integrator is responsible for managing the device service life through an electronic components management plan, taking into consideration the information contained within the device selection safety net considerations. These device selection safety net considerations are detailed in sections 4.1.1 through 4.15.

#### 4.1.1 First-Time Use.

The first time a COTS microprocessor is selected for use in an aircraft system it should be evaluated with great attention to detail. Consider the following relevant questions: How long has the microprocessor been fielded? What has it been used for? Is there substantiated service history that can be evaluated? Additional care should be considered in the evaluation of its availability estimates (see section 4.1.2), stability evaluation (see section 4.1.3) and suitability (see section 4.1.4). The length of time the microprocessor has been fielded, the number of microprocessors currently in use, and the number of existing applications for that microprocessor provide insight during the selection process.

#### 4.1.2 Availability.

Availability focuses on the maturity of the device and includes libraries, tape-out iterations, launch customer, and number of units currently fielded. The review attempts to discover unknowns as related to the manufacturers' intended use. The maturity of the manufacturers' supporting libraries can provide insight to determine when a device could become suitable for use and when variation is less likely to occur.

Tape-out maturity can provide an indication of where the manufacturer is within their development cycles. Manufacturers typically plan on several tape-outs prior to production release for the purpose of incrementally debugging the device operation and fabrication. Using a device with fewer tape-outs, as measured against the manufacturer's normal number of tape-outs, can indicate the risk of the manufacturer making changes without notifying the customer.

Interviewing initial customers of a COTS microprocessor and assessing their applications associated with the device can provide insight to the device maturity level as driven by the in-service use. Initial in-service use has become a debugging tool employed by manufacturers. In today's rapidly changing environment coupled with demands by customers that are not in the aerospace industry, manufacturers are generally given less time to extensively debug a product compared to past years. Industry trends indicate that the first generation use of a newly released device is less stable, thus requiring changes to be made by the manufacturer in most cases without the requirement to inform the users.

# 4.1.3 Stability.

Assessment of the device life cycle history can provide insight into the microprocessor's stability based on publicly available data, such as application notes and errata sheets. Microprocessors that are variations of an existing family may exhibit early operational stability versus a device that is not based on an existing family of devices.

#### 4.1.4 Suitability.

Suitability involves the review of the intended application against the manufacturer's published performance data. When using microprocessors, available useful performance (actual rates) should be expected to be less than that implied by raw clock rates (published rates). Reasons for the decreased available performance includes the following: cache miss rate, interference between multiple execution units running simultaneously in parallel, and instructions that require multiple clock cycles to complete. In addition, the microprocessor manufacturer's fabrication process uses proprietary libraries that are intentionally not disclosed to customers and are accounted for in the overall performance and fabrication process.

Microprocessor startup times are an important aspect of suitability due to the stringent availability requirements for commercial avionics. If the microprocessor must be restarted due to error conditions during operation, the microprocessor startup time should be well understood when selecting devices and constructing safety nets. The following restart conditions should be considered for the safety net design:

- Time constraints for startup should cover all possible startup conditions based on the system design, design assurance level, and required response.

- Time constraints for startup should include the microprocessor configuration initialization time and any required initialization to satisfy system safety requirements.

Another important aspect of suitability involves the manufacturer changing device package sizes without making any additional changes, other than possibly core voltage. For example, experience has shown that a device that was manufactured in a 90-nanometer process and migrated to a 60-nanometer process will likely demonstrate a change in characteristics. There is no guarantee that simply changing package size will not cause a change in the application's performance and operation; and significant evidence shows that it can.

Another key area of suitability is the demonstration of an acceptable understanding of the embedded features within the device and the intended use. For those features that are not intended to be used, it has been expressed by the regulatory agencies that the integrator must demonstrate an acceptable understanding of potential misbehavior caused by the activation of an unused function. Additionally, the integrator must include the mitigation for disabling or deactivating a given feature.

#### 4.1.5 Testability.

Tests to characterize device behavior and performance are typically performed at many levels, beginning with the manufacturer data. Designers may use configurable cores within their system that may not provide full visibility into their behavior due to encryption or other intellectual property limitations. The manufacturer's intended testability approach may not provide enough insight, may not be consistent with the integrator's testing approach, or may not be suitable for the intended application. Industry experience has shown that an unexpected behavior can occur with a difference in testing approaches between the integrator's expectation and the manufacturer's intentions. Some proven techniques for characterizing device behavior are:

- Manufacturer's intended testability approach

- Error-correcting code

- Built-in self test (BIST)

- Automatic test pattern generation

The multilevel safety net approach defined in section 4.2 encompasses safety compliance at various levels as appropriate to the associated safety risk. Research conducted reveals the escalating future impracticality of ensuring safety at the device level alone when COTS microprocessors and equivalent airborne electronic hardware technology are used [4].

#### 4.2 SAFETY NET MONITOR CONSIDERATIONS.

The term safety net monitor is intended to convey technology approaches that could be employed through the use of hardware and/or software solutions. The safety net methodology presumes the device will misbehave during its service life, and therefore, the safety net monitors would likely need to be architecturally integrated at a level above the device itself.

It is the intent of this Handbook to help identify some safety net monitors that were discussed and/or physically tested through example design. The responsibility for defining and using safety net monitors belongs to the integrator developing the application-specific architecture.

#### 4.2.1 Hardware Monitor Considerations.

Hardware monitors focus on hardware-based technology solutions to indicate when unexpected changes in behavior or physical characteristics occur. The list below identifies the types of

hardware monitors discussed during the research. It is recognized that some of these considerations could also be implemented using software applications.

- Memory (parity/error correction code/SEU monitors)

- Internal buses (address and data parity)

- External buses (protocol checks, parity, checksums, activity patterns, cyclic redundancy code)

- Discrete digital signals (dualize I/O, BIT stimulation capability, wraparounds)

- General signals (wraparounds analog/digital to digital/analog, range checks, rate checks, etc.)

- Dissimilar hardware (address generic hardware fault coverage)

- Configuration register monitors

#### 4.2.2 Software Monitor Considerations.

Software monitors focus on software application solutions to indicate when unexpected changes in behavior or physical characteristics occur. The list below identifies the types of software monitors discussed during the research. To better support the safety net methodology, the application-specific architecture would need to consider the risk of the microprocessor misbehaving and having an adverse effect on the monitor's ability to accurately report abnormal behavior.

- Additional system-level and box-level built-in-test (SBIT: Start-up BIT; IBIT: Interface, initiated, interruptive, or intermittent BIT; PBIT: Periodic BIT; MBIT: Maintenance BIT)

- Additional voting planes

- Data integrity checks

- Configuration register monitors

# 4.2.3 External Monitor Considerations.

External monitors are identified below where each microprocessor has its own custom dedicated watchdog monitor (WDM) for reporting abnormal behavior.

WDM power up failed and must be properly serviced to be declared valid.

- WDM should be serviced once per frame.

- WDM has an independent clock source and voltage rail.

- WDMs are designed with custom requirements to the processor, design configuration, criticality, and the utilization.

- WDM failures are reported through cross-channel data links to the other channels and voting planes.

The following are types of techniques discussed as potential solutions during the research, but this list is not exhaustive.

- External monitoring of safety-related behavior

- External redundancy

- External watchdogs

- External architecture that allows a level of autonomous run-time correction

#### 4.2.4 Internal Monitor Considerations.

The research acknowledges the use of internal monitors from the aspect of those that can be embedded, such as BIST, at the transistor level as associated with a multicore device. The level of research conducted with internal monitors was limited to the association of software monitors discussed in section 4.2.2.

#### 4.3 ARCHITECTURAL SAFETY NET EXAMPLES.

The architectural safety net examples in sections 4.3.1 through 4.3.5 were identified by research as possible approaches and are discussed only briefly. The details behind using these examples are understood to be the responsibility of the integrator, as applicable to the application-specific solutions. These examples are not meant to be a complete list of approaches, as application-specific solutions may differ greatly from these examples. It is not the intent of the research or this Handbook to provide implementation details.

#### 4.3.1 Shared Resource Approach.